NTDPJTV01

"Customer Satisfaction Through Knowledge"

SERVICING

PROJECTION

**TELEVISION**

**TOSHIBA AMERICA CONSUMER PRODUCTS, INC.**

"In Touch with Tomorrow"

## FOREWORD

The material presented in this manual is for technical training purposes only.

Some of the circuits discussed are not utilized in all models.

The schematic diagrams included are simplified for training purposes and should not be used for actual troubleshooting.

Always refer to the proper service manual by model number whenever performing service or adjustments.

This material was prepared by the National Training Department of Toshiba America Inc.

## TABLE OF CONTENTS

IV.

## I. INTRODUCTION

| General  | Informa | tion | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | 1 |

|----------|---------|------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Features | • • • • |      | •• | • | • | • | • | • | • | • | • | • | • | • | • | • | 3 |

| Block D  | iagram  |      |    |   |   |   |   |   |   |   |   |   | • | • |   |   | 6 |

## II. POWER SUPPLY

| Standby Power Supply | • | • | • | • | • | • | • | • | • |   | • | • | 7  |

|----------------------|---|---|---|---|---|---|---|---|---|---|---|---|----|

| Main Power Supply    |   | • | • | • | • | • | • | • | • | • |   |   | 13 |

| Sub-Power Supply     |   |   | • | • | • |   | • | • | • | • | • |   | 17 |

#### **III. SYSTEM CONTROL**

| Tuning Control Microcomputer | 20 |

|------------------------------|----|

| D/A Control                  | 26 |

| Non-Volatile Memory          | 28 |

| Port Expansion               | 31 |

| On-Screen Display            | 36 |

| VIDEO/CHROMA PROCESSING        |    |

|--------------------------------|----|

| Tuner, PIF, AGC                | 41 |

| Video Processing Overview      | 47 |

| Video/Audio Input Switcher     | 49 |

| Vertical Contour & Comb Filter | 51 |

| S-VHS Video Switching          | 53 |

| Picture Sharpness              | 55 |

| Black Stretching               | 57 |

| ABCL & ABL                     | 59 |

| Chroma Amp, ACC, APC           | 65 |

| Color Killer & Demodulator     | 69 |

#### TABLE OF CONTENTS (con't)

#### **V. PICTURE IN PICTURE**

| PIP System              | 72 |

|-------------------------|----|

| Video/Chroma Processing | 74 |

| A/D Converter           | 76 |

| Write/Read Data         | 79 |

| Table 1                 | 80 |

### VI. MTS BROADCASTING SYSTEM

| Theory of Operation | 83 |

|---------------------|----|

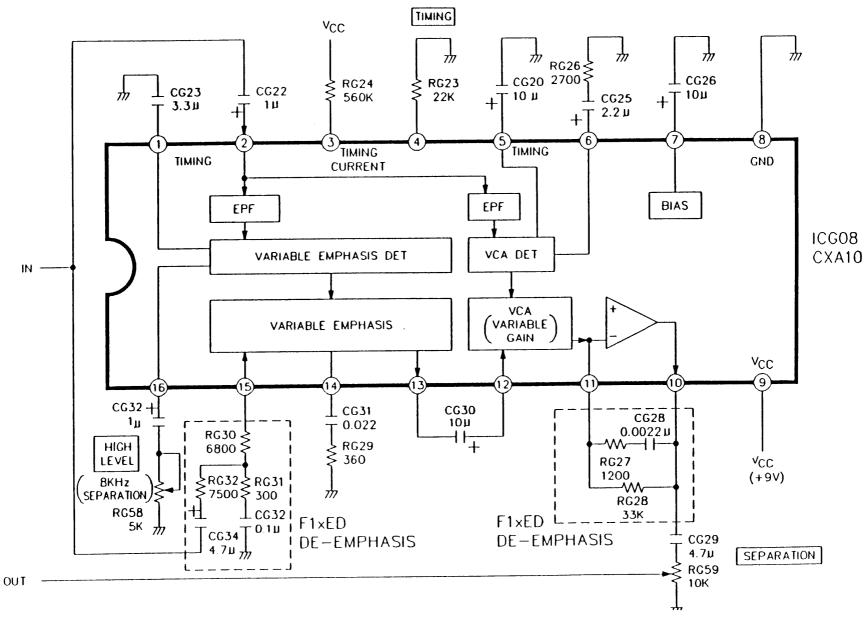

| MTS Demodulator     | 85 |

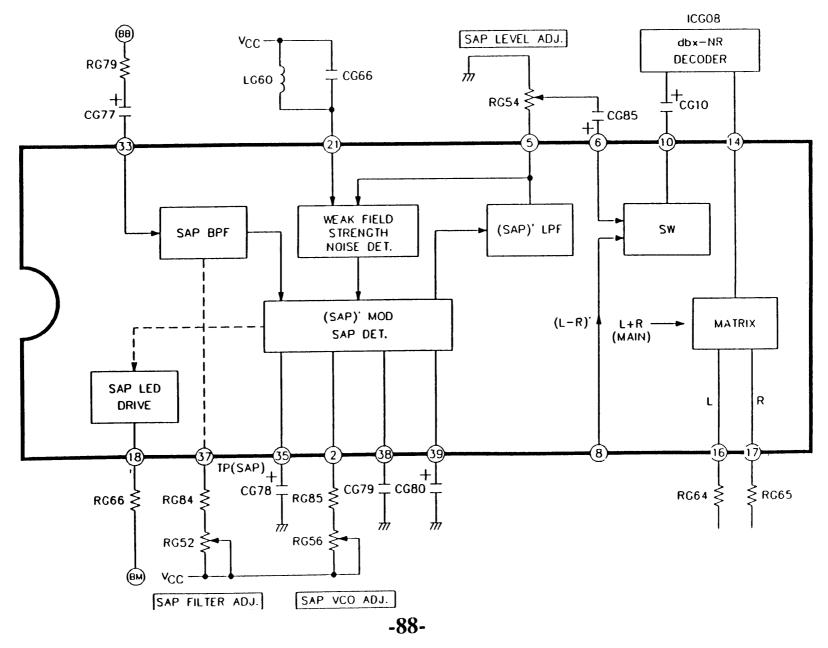

| SAP Demodulator     | 87 |

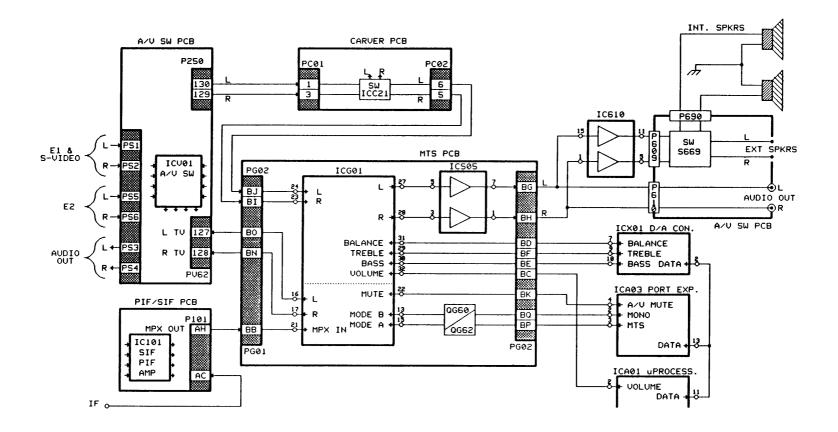

## VII. AUDIO PROCESSING

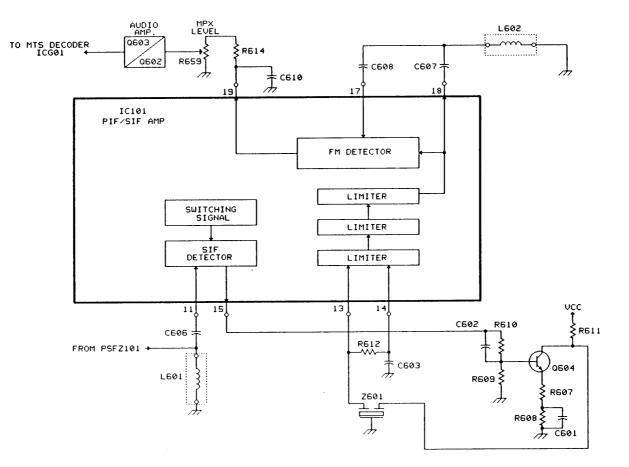

| SIF                         | 92 |

|-----------------------------|----|

| Audio Circuit Outline       | 94 |

| Volume/Tone Control Circuit | 96 |

#### VIII. CARVER AUDIO

| Carver Audio Outline               |        |

|------------------------------------|--------|

| Operation of Carver Audio Circuits | <br>99 |

#### IX. VERTICAL DEFLECTION

| Vertical Deflection & Output  | 106 |

|-------------------------------|-----|

| Vertical Linearity Correction | 112 |

| Vertical Protection Circuit   | 114 |

## TABLE OF CONTENTS (con't)

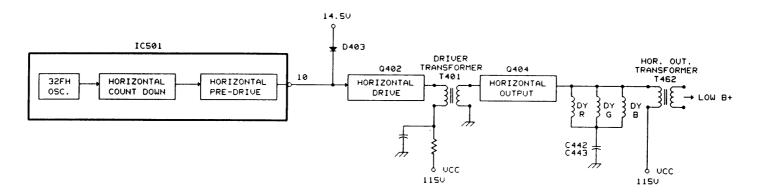

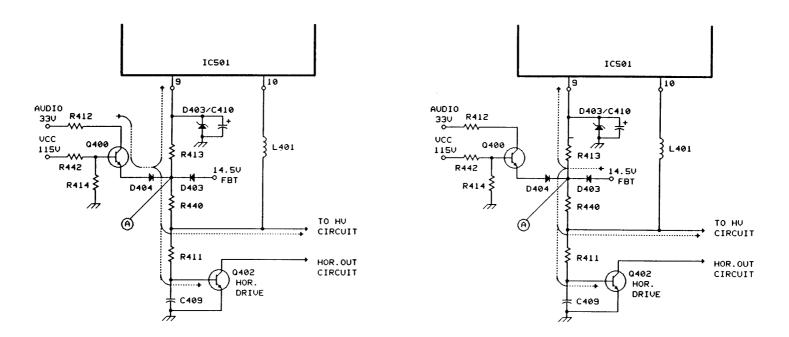

## X. HORIZONTAL DEFLECTION

| Horizontal Start Up             | 117 |

|---------------------------------|-----|

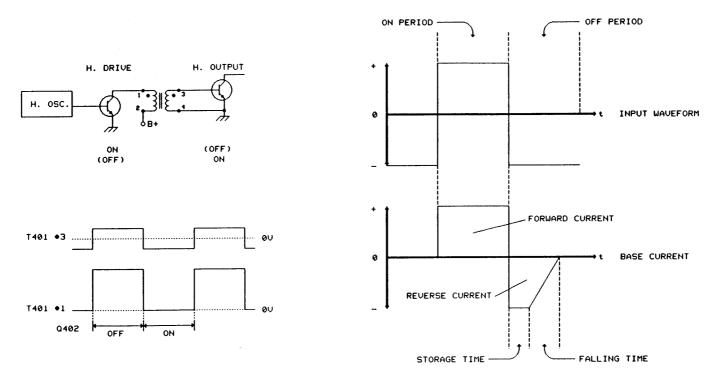

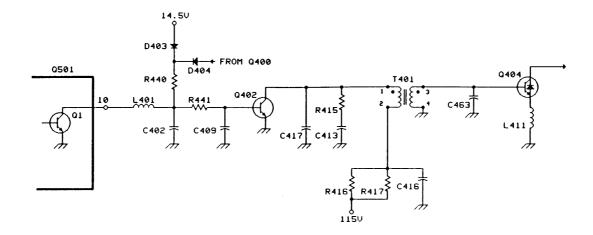

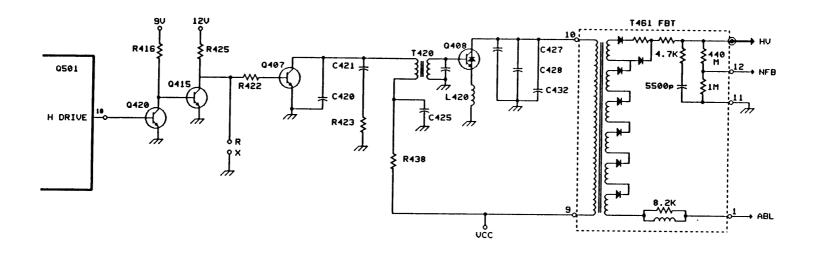

| Horizontal Drive                | 121 |

| Horizontal Output               | 125 |

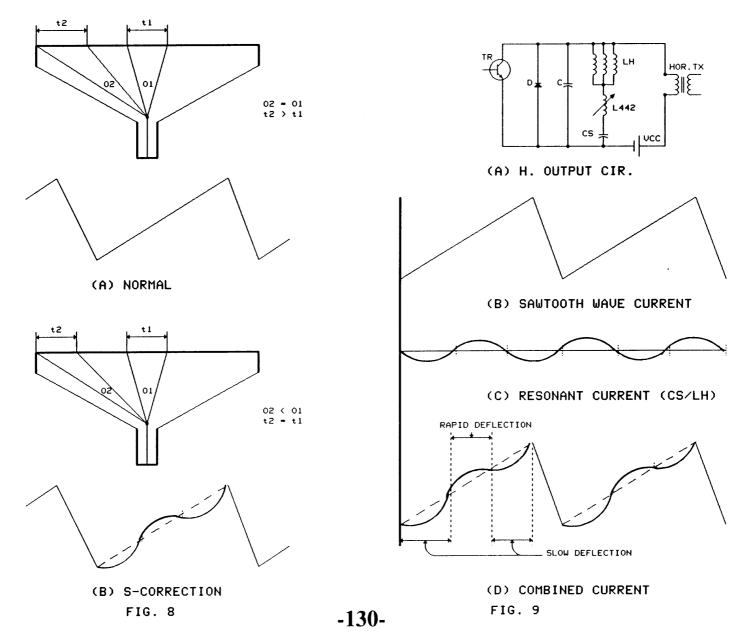

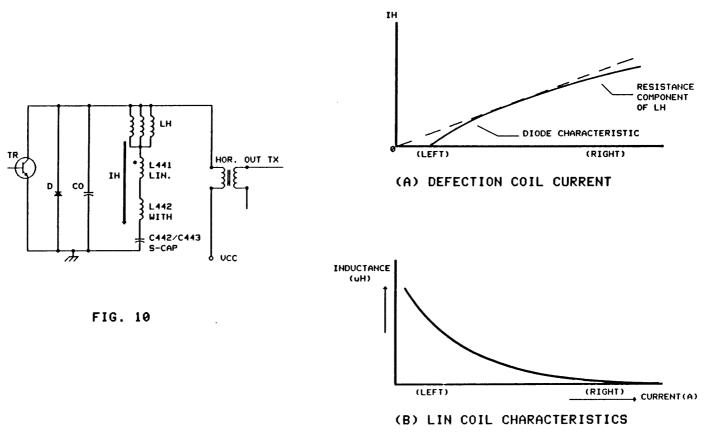

| Horizontal Linearity Correction | 129 |

| Low Voltage Generation          | 133 |

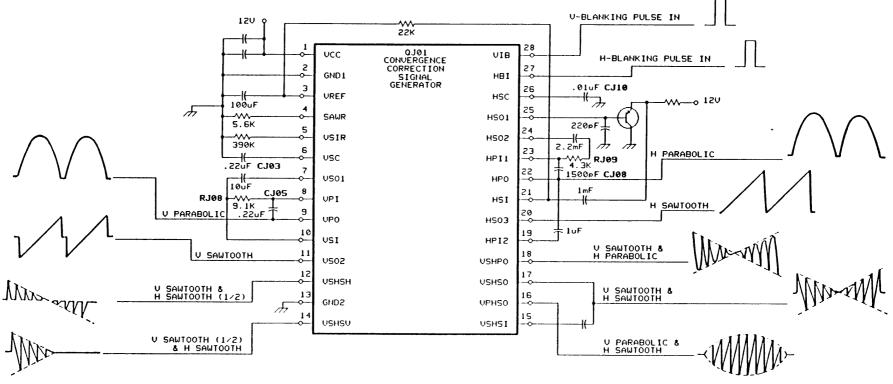

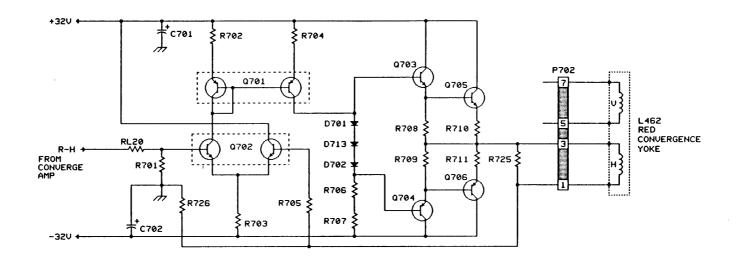

| Convergence Signal Generation   | 135 |

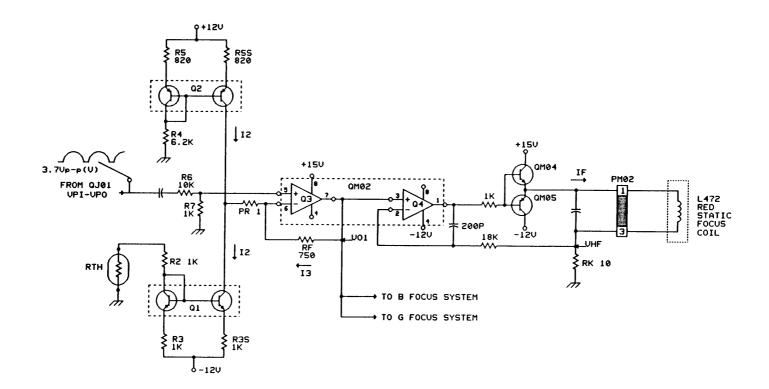

| Focus                           | 141 |

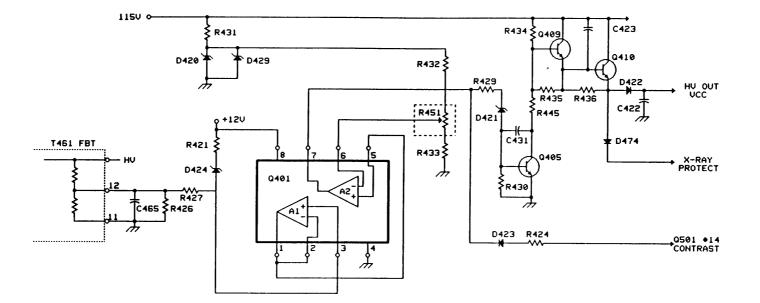

## XI. HIGH VOLTAGE

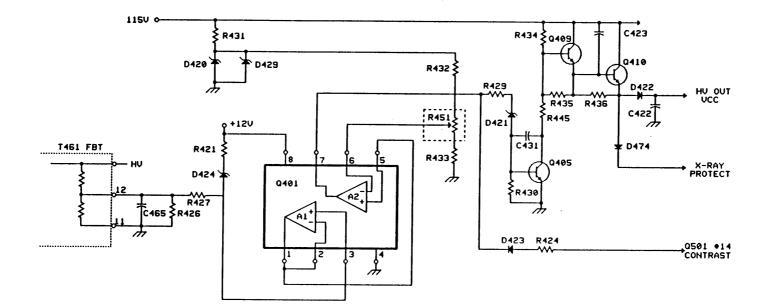

| High Voltage Generation    | 143 |

|----------------------------|-----|

| High Voltage Stabilization | 145 |

| X-Ray Protection           | 149 |

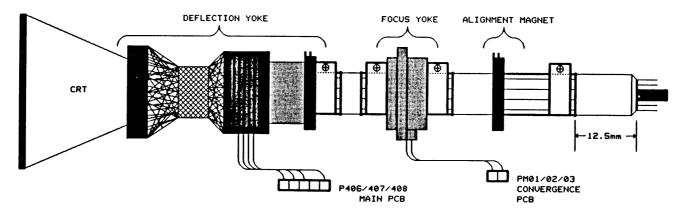

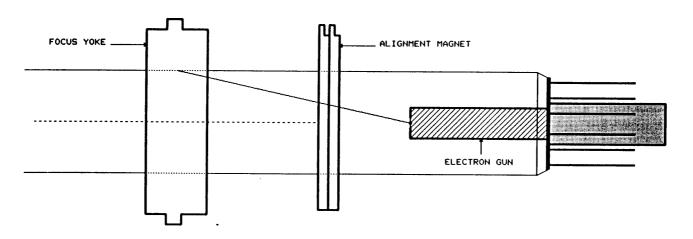

| XII. | OPTICAL SYSTEM            |

|------|---------------------------|

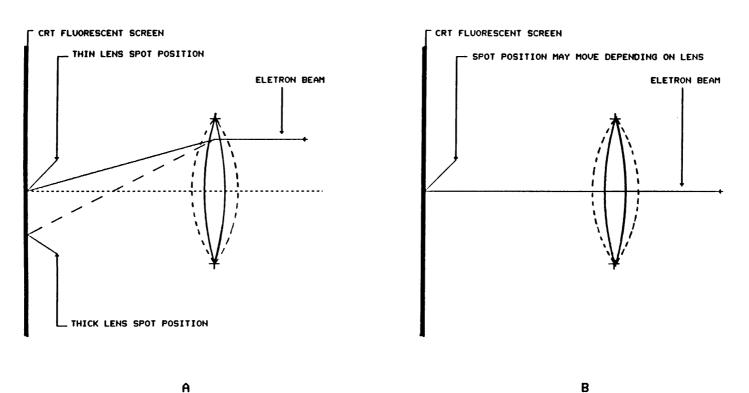

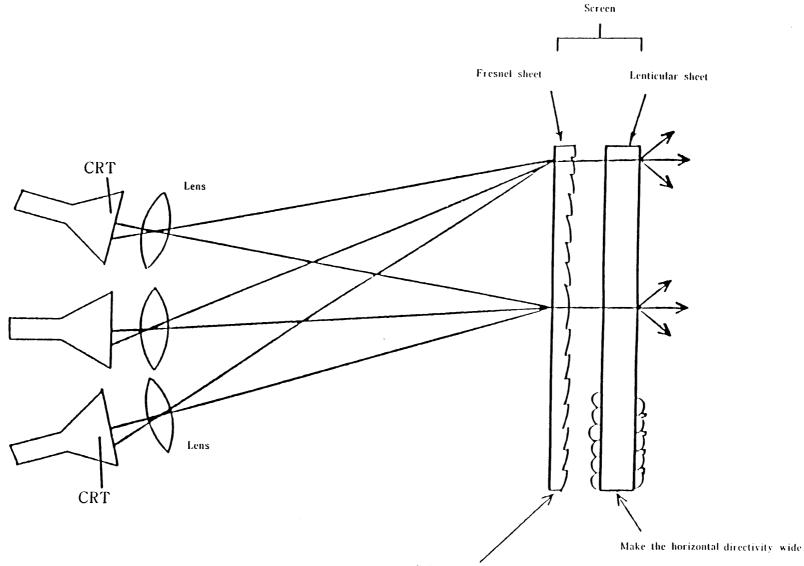

|      | CRT Outline 152           |

|      | Viewing Screen Affect 156 |

| XII. | LAB                       |

|      | TROUBLESHOOTING           |

|      | HORIZONTAL 157            |

|      | VERTICAL 161              |

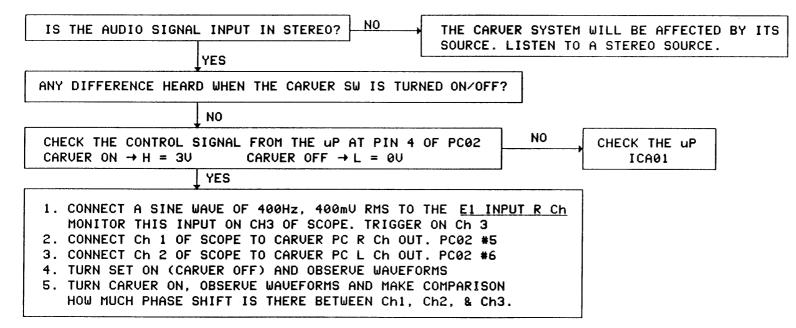

|      | CARVER AUDIO 163          |

|      | PIP 164                   |

|      | POWER SUPPLY 165          |

|      | HANDS-ON                  |

|      | Chassis Removal 166       |

|      | CRT Adjust 167            |

|      | Convergence 169           |

|      | Gray Scale 174            |

iii

I.

## INTRODUCTION

### **GENERAL INFORMATION**

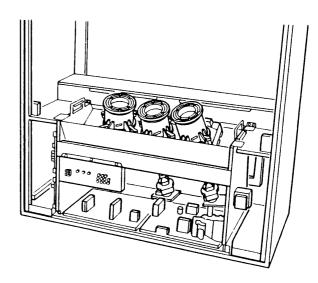

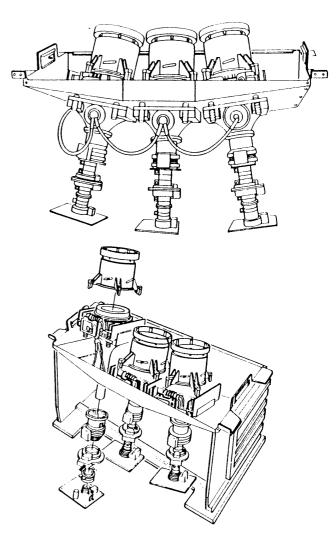

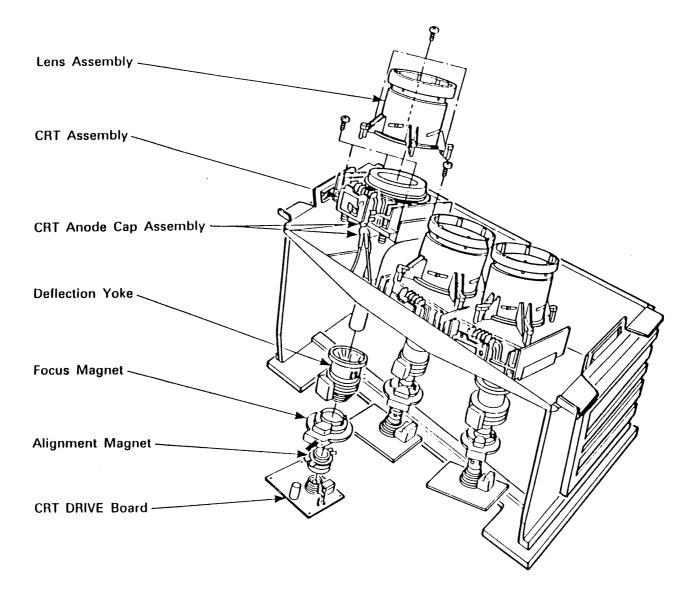

There are three new 7" cathode ray tubes inside Toshiba's giant 46" and 52" projection television sets, producing superior resolution and brightness thanks to a new type of phosphor that greatly improves radiation efficiency. Brightness now increases linearly in proportion to increased voltage, unlike the standard phosphor. In addition, the electron beams are accelerated to strike the phosphor harder. The results is a picture that is 25% to 30% brighter than conventional projection sets. A higher horizontal resolution of 560 lines has also been achieved through the new Electron beam, producing a spot that is 50% smaller and more intense. These changes are particularly impressive during the time of white peak. In addition, images are now just as sharp on the edges as they are in the middle, the result of a new Dynamic Focus System. As the beam scans from one edge...to the center...to the other edge, an adjustment is made in the lens that takes into account the distance between the lens and the screen surface.

The projection television uses the X-63G chassis which has a main PC board on which three PC boards are vertically mounted. The function of each board is listed below.

\* PIF and SIF Board

\* CCD Comb Filter

\* MTS Board

In addition, there are the following PC boards which are mounted throughout the cabinet.

\* Carver Audio Board

\* Audio/Video Board

\* PIP Board

\* Power Supply Board

\* Convergence Board

\* CRT Drive Boards (3)

Should any modifications be required in the future, they will be made to the individual PC boards.

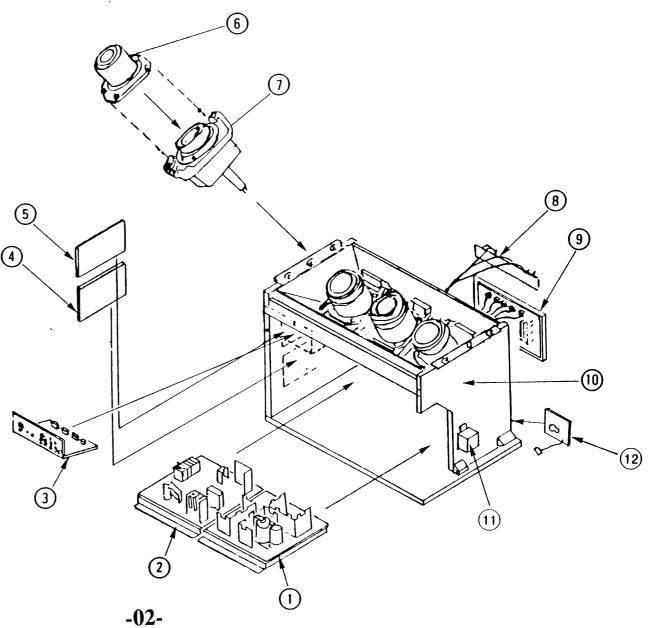

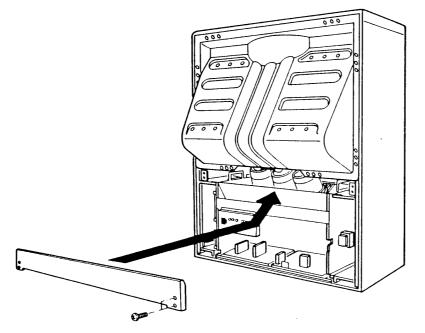

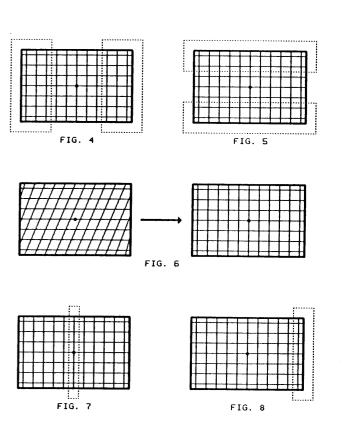

## CHASSIS CONSTRUCTION

- 1) POWER PCB

- 2) MAIN PCB

- 3) A/V INPUT PCB

- 4) CARVER AUDIO PCB

- 5) PIP PCB

- 6) MAIN LENS

- 7) CRT ASSEMBLY & OPTICAL COUPLING (R) (G) (B)

- 8) FRONT CONTROL PANEL

- 9) CONVERGENCE PCB

- **10) LIGHT BOX**

- **11) POWER TRANSFORMER**

- 12) CRT DRIVE PCB (R) (G) (B)

## FEATURES AND SPECIFICATIONS

## MODELS

## **TP4648**

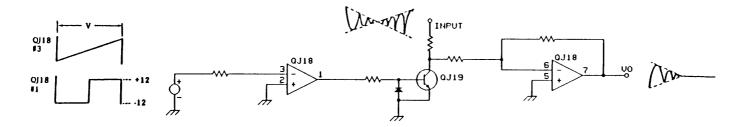

## **TP5288**

Out

| Screen Size             |                   | 52"               |

|-------------------------|-------------------|-------------------|

| Viewing Angle           | H: 120 /V: 20     | H: 120 /V 20      |

| Horizontal Resolution   |                   | 560 Lines         |

| Peak Brightness Level   | >300 foot-lambert | >300 foot lambert |

| Hybrid Lens System      | yes               | yes               |

| Optical Coupling System | yes               | yes               |

| Channels                | 181               | 181               |

| RF Inputs               | 2                 | 2                 |

| Unified Remote          | 50 key            | 50 key            |

| PIP                     |                   | 1/4 & 1/16        |

| PIP Swap                | yes               | yes               |

| PIP Still               | yes               | yes               |

| PIP Position Change     | yes               | yes               |

| PIP Channel Search      | 4 Channels        | 4 Channels        |

| PIP Sequential picture  | 4 Frames          | 4 Frames          |

| Peak-ACL/ABCL           |                   | yes               |

| Off-Timer               | 180 min. max.     | 180 min. max.     |

| Program Scan            |                   | yes               |

| Comb Filter             | ĊCD               | ĊCD               |

| A/V In/Out              |                   | 2-A/V In, 1-A/V O |

| S-VHS Input             | yes               | yes               |

| Var. Audio Out          | yes               | yes               |

| Audio Output            |                   | 12W               |

| Surround Audio          | Carver            | Carver            |

| MTS (STR/SAP/MONO)dbx   | yes               | yes               |

| On-Screen Display       |                   | yes               |

-03-

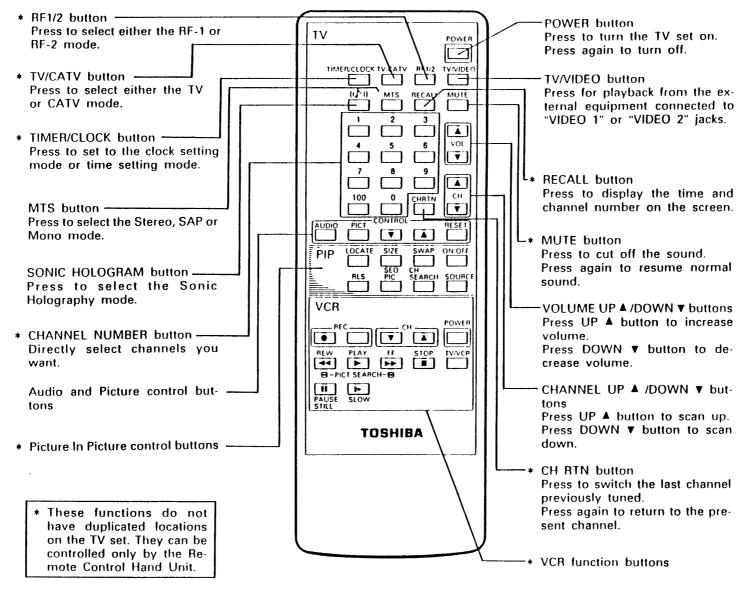

## **REMOTE CONTROL HAND UNIT**

-04-

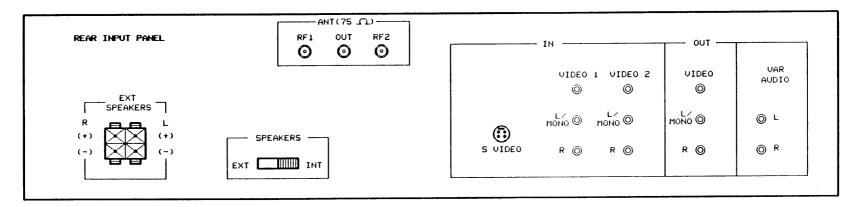

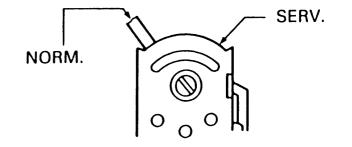

## FRONT AND REAR CONTROLS.

۰ ۰

.

RMT SONIC ON/OFF POWER SENSOR HOLOGRAPHY STR SAP FRONT CONTROL DISPLAY (ORN) (YEL) (GRN) (ORN)

| rol, pane<br>Ie of doc |                   |       |           |        |          |     | SONIC<br>HOLOGRAF |              | TU/<br>VIDEO | uo∟<br>♥<br>Ø | UME | сна<br>•<br>2 | NNEL  |

|------------------------|-------------------|-------|-----------|--------|----------|-----|-------------------|--------------|--------------|---------------|-----|---------------|-------|

|                        | TEST<br>ON<br>OFF | COLOR | тінт<br>О | BRIGHT | CONTRAST | MTS | ADD/<br>ERASE     | AUTO<br>PROG |              | CON<br>•      |     |               | RESET |

-05-

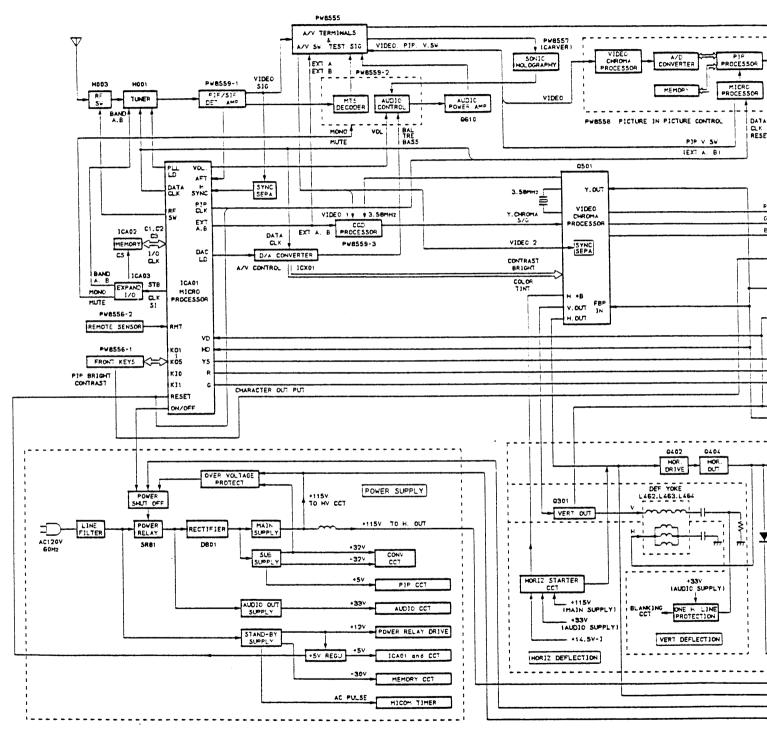

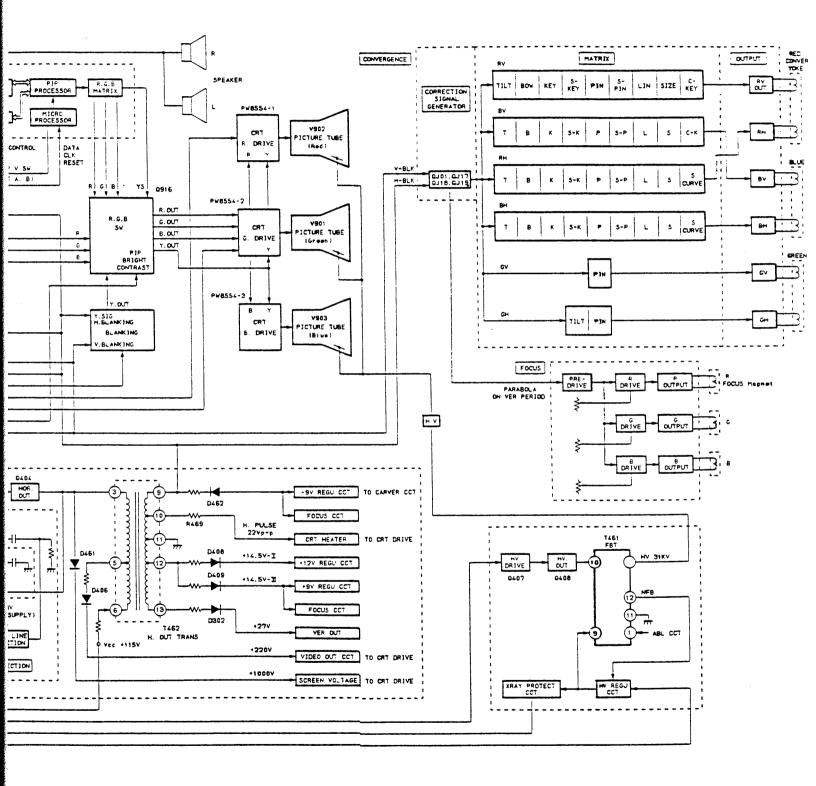

#### CIRCUIT BLOCK DIAGRAM

6

# II. POWER SUPPLY

-II-

## **POWER SUPPLY CIRCUITS**

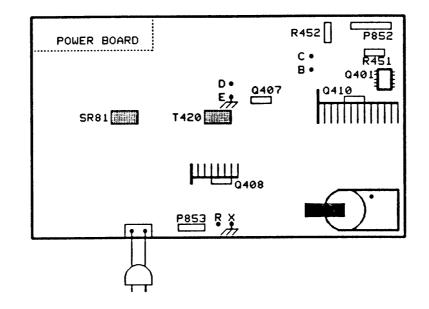

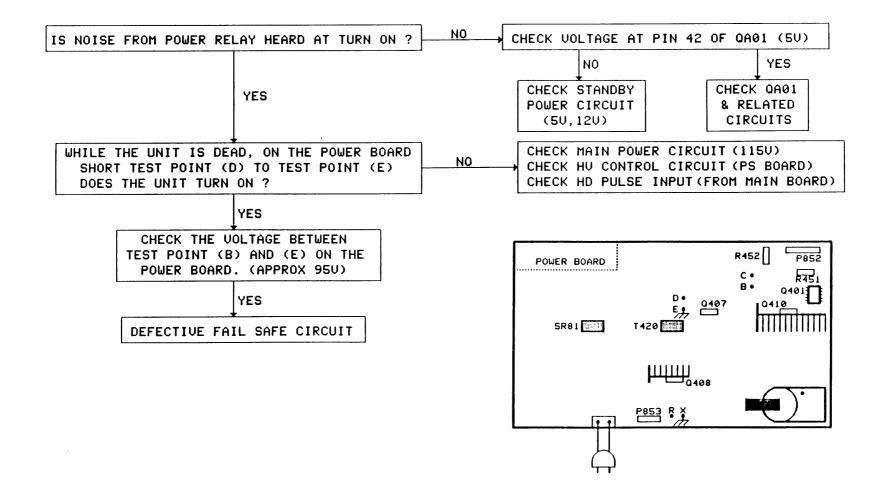

The power supply circuits for the TP4688 and TP5288 are mounted on the POWER SUPPLY PC BOARD and consists of the following 4 power supplies:

(1) The Standby Power Circuit (Switching Type).

This power circuit will provide the "Keep-alive" Voltages. -30V to the Non-volatile Memory Circuit, +5V for the uP and Remote Circuit and provides reset to the uP. Also, +12V is supplied to the power relay.

(2) The Main Power Circuit (Switching Type).

This power circuit provides the +115V to both the Horizontal Output Circuit in the Main PCB, and the H V Circuit in the Power PCB.

(3) The Sub-power Circuit (Switching Type).

This power circuit provides the +/-32V to the Convergence Circuit and +5V for Picture In Picture Circuit.

(4) The Audio Out Power Circuit (Linear Type).

This power circuit provides +33V for the Audio Circuit and Horizontal Start-up. It consists of the power transformer T864 (mounted on right side of light box) and the bridge rectifier circuit on the PS Board.

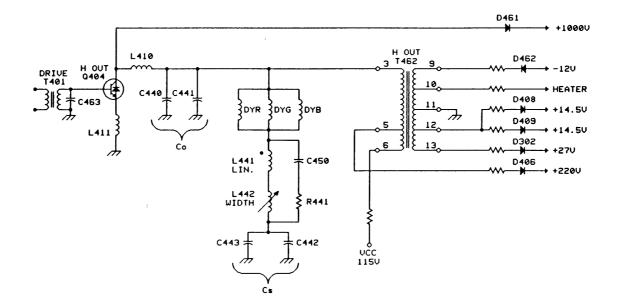

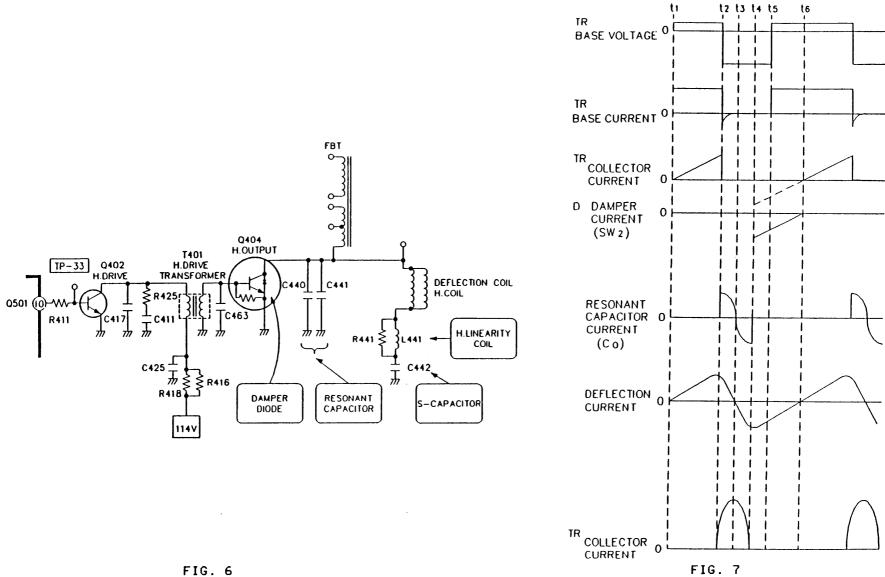

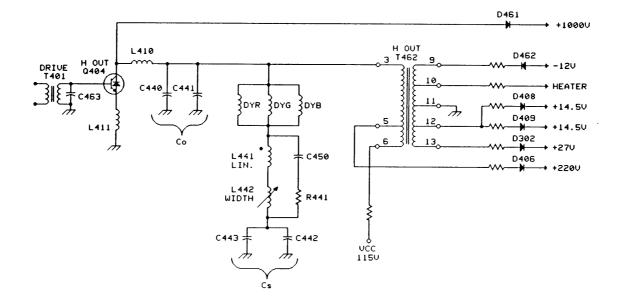

In addition, several scan-derived supplies are provided by the fly-back transformer T462 of the Horizontal Deflection Circuit. These voltages are covered in the Horizontal Output section of this manual.

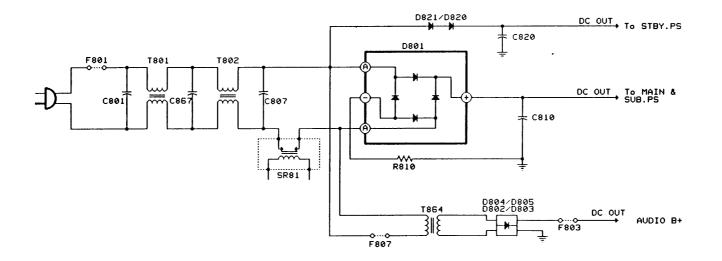

Starting at the AC input is the Rectifier Circuit (See Fig.1). Here the AC supply voltage is filtered by T801/T802 and coupled to T864 of the Audio B+ Circuit. One leg of the AC supply is rectified by diodes D820/D821 and filtered by C820. This DC output is supplied to the Stand-by Power Circuit. Another leg of the AC supply goes through power relay SR81 and on to the AC input terminals of the bridge rectifier block D801. The rectified output from D801 is filtered by C810 and supplied the Main and Sub-Power Supply Circuits. R810 will limit any current surges that will occur when the unit is turned ON.

## **RECTIFIER CIRCUIT**

.

FIG. 1

-08-

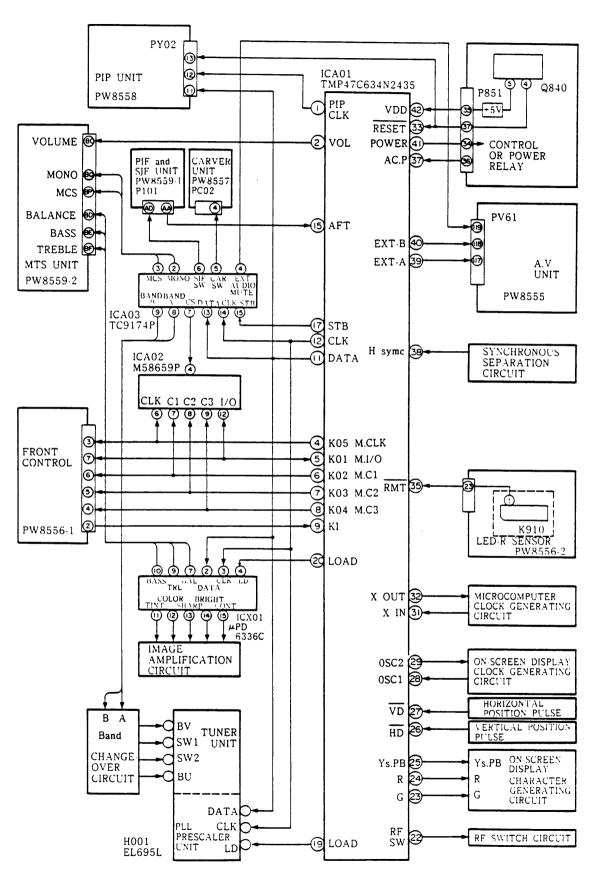

## THE STANDBY POWER SUPPLY

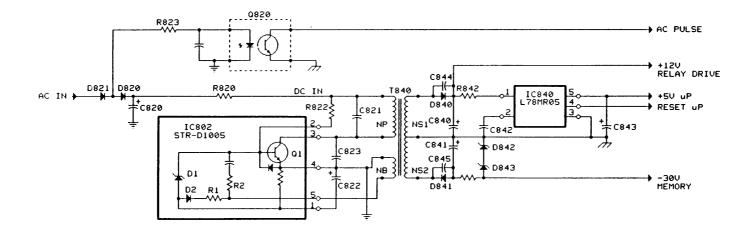

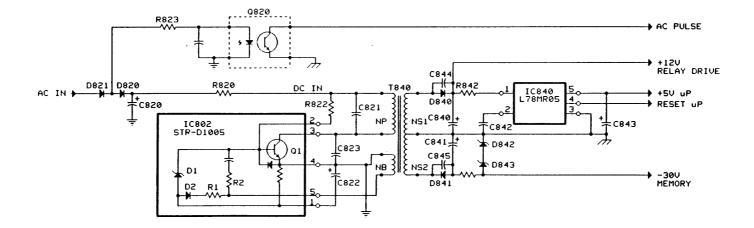

The Standby Power Supply provides the "Keep-alive" Voltages. They include +12V to the Power Relay, +5V to the Main Microprocessor IC & Remote sensor as well as -30V to the Memory IC. Reset to the Main uP is also developed here.

The Standby Power Supply Circuit consists of a Self-excited Converter type ringing choke which uses a Hybrid IC (STR-D1005) as the Switching Regulator IC. D820, D821 and C820 work as a half wave rectifier circuit and develop the Input DC voltage. Also, a rectified AC pulse from D821 is supplied to the photo-coupler IC820 which produces an AC pulse that is used in the timer operation of the Microcomputer.

When the Input Voltage is applied to IC802 pin 2, Q1 Base Current flows through start-up resistor R822 and Q1 turns ON. Now the Input Voltage will flow through the primary winding (NP) of transformer T840, into IC802 pin 3, through Q1, to ground. This induces a voltage through the secondary winding (NB). This induced voltage causes current to flow through C822, into IC802 pin 1, through D2 and back out through pin 5. This current also flows up through R2 to the base of Q1, which increases the base current (IB) of Q1 further, and finally IB will reach a constant value, (saturation point). At the same time the collector current (IC) of Q1 will increase proportionally with time. This current increase however can not be maintained after a time when IB<IC. As a result, the voltage across the NP winding ceases to increase thereby stopping the build-up of magnetic flux and causing a decrease in voltage across the NB winding. The decrease in voltage across the NB winding is going to decrease the current flow up through R2 to the base of Q1. Now the base current (IB) decreases and Q1 is turned off rapidly. At the moment that Q1 is turned off, reverse EMF (with the polarity inverted) occurs on each winding of the transformer. The energy stored in the transformer is the same as it was just before Q1 was turned off. This energy is supplied to the load.

## STANDBY POWER SUPPLY CIRCUIT

FIG. 2

#### **STANDBY POWER SUPPLY (CONT.)**

During Q1's off period, C822 is charged through D2 from the NB winding, and this voltage will be negative. It will cause D1 to conduct and the base current (IB) will flow towards D1, thereby keeping Q1 off.

Furthermore, the period in which current is flowing into C822 is the same as the period in which the secondary coil of T840 is supplying power to the output circuit. The voltage at the secondary (VO) is proportional to the charge voltage (VC) at C822. This is how voltage regulation is performed. If the output voltage goes up, this increase will cause an increase of current flow on the secondary winding (NS), the current flow at NB will also go up, but because the NB winding is inverted, the current flow will be negative. This negative current flow will be felt at the anode side of D1 causing it to conduct ahead of time which in turn will turn off Q1 faster than normal. This causes the duty cycle of NP to be shorter, which in turn will lower the voltage on the secondary side. If the output voltage was to go down, the above procedure will take place in reverse.

Notice that on this particular power supply, theoretically the frequency is not adjustable. Only the duty cycle is adjustable.

On the secondary side of T840, Capacitors C844, and C845 are used to prevent spurious diode radiation. D840 & C844 make up a +12V rectifier circuit. D841 & C845 make up a -30V rectifier circuit.

R842, and IC840 (voltage control IC L78MR05) are part of a DC/DC Converter, which provides the uP + 5V & the initial reset.

## STANDBY POWER SUPPLY CIRCUIT

FIG. 2

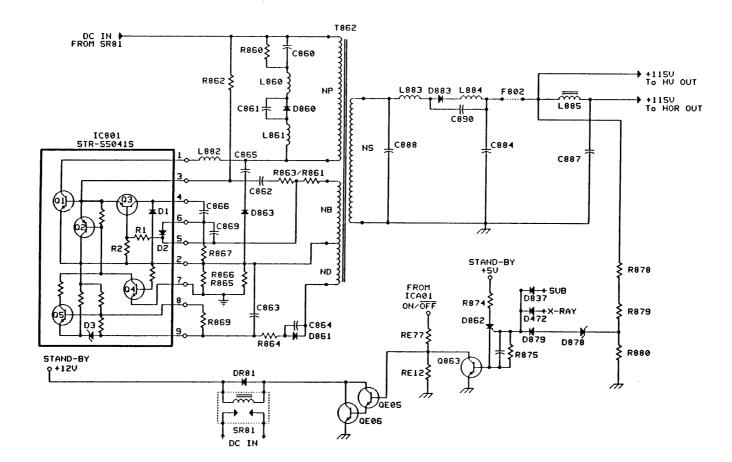

## THE MAIN POWER SUPPLY

The Main Power Supply provides 115V output to the Horizontal Output Circuit on the Main Board, and to the High Voltage Output Circuit on the PS Board. This power supply is called an "Automatic Voltage Regulator".

The Main Power Supply Circuit, like the Stand-by Power Circuit, consists of a Self-excited Ringing Choke Type Converter. It uses a Hybrid IC (STRS5041S) for a Switching Regulator IC801.

When the Input DC Voltage is applied to IC801 pin #3, Q1 base current (IB) flows through the Start Up Resistor R862 and Q1 turns ON. During the Q1 ON period, current flows through the Primary Winding (NP) of the Transformer T862. Then a voltage with the opposite polarity as the Primary Winding (NP) will be induced on the Secondary Drive Winding (NB). As a result, C866 will be charged through a loop made up of D1, C866, D2, and R861. While Q1 is in the ON period, Q3 is forward bias by the charge stored in C869 which is rectified by D2 and applied to the voltage divider of R1/R2, so now Q1 base current will flow from C866, through Q3, and R867. This causes Q1 to coduct very hard towards saturation. When the Base Current (IB) reaches a specified value which is proportional to the Input Voltage (E in), the collector current (IC) would have reached Q1's saturation point. Now the voltage across the primary winding (NP) ceases to increase thereby stopping the buildup of magnetic flux and causing a drop in voltage across the secondary winding (NB). The voltage drop across the NB Winding will reduce the base current of Q1 and thus Q1 is turned OFF. Now the energy stored in T862 is transferred to the output load. When the current supplied to the load falls to zero, the voltage across the winding of T862 develops a ringing voltage. The same kind of voltage will also be induced in the Drive Winding (NB). When the ringing voltage changes from zero to the next half cycle, a recovery current at the Diode D863 flows and this allows a forward bias to flow through the Q1 Base-Emitter instantly. With this biasing operation, Q1 will turn ON again. Hereafter, the same operations are repeated, thus oscillation will continue.

Accordingly, if the AC Line voltage drops, causing the voltage across the NB Winding to drop, a constant base current will be supplied to Q1 during the ON period from the charge stored in C866. So C866 helps to stabilize the oscillation by determining the time constant, which it does by boosting the collector voltage of Q3.

## MAIN POWER SUPPLY CIRCUIT

FIG. 3

-14-

18 M

#### MAIN POWER SUPPLY (CONT.)

The ND Winding (Detection Secondary Coil) and the NS Winding is provided to control the stability of the power supply. D861, R864, and C863 work as a rectification circuit and develops a Detection Voltage of -42 volts. When the secondary voltage increases, the voltage across the secondary detection coils also increases. This will increase the voltage across C863 (-42V line) which will turn ON D3 and depending on the value of R869 will turn ON Q5 which in turn will turn ON Q2. This will Cut-Off Q1, thus stabilizing the output voltage with a shorter ON cycle. This is the Voltage Monitor Operation.

The Q1 Collector Current outputs from pin 2 of IC801 and flows into R865/R866 (Monitor Resistors). In the event that the current goes high, Q4 is turned ON through an internal resistor, turning Q2 ON and cutting OFF the base of Q1. At this time the output voltage will drop. This is The Over Current Protection Circuit.

#### THE SECONDARY CIRCUIT

D883, C884, L883 and L884 rectify and filter the +115V Out to the Horizontal Output and the HV Output Circuits.

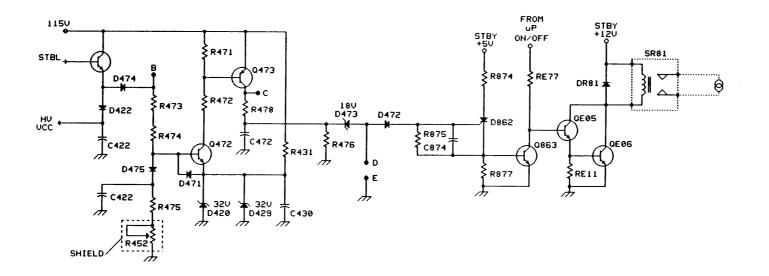

R878, R879, and R880 are Over Voltage Detection Resistors. Zener Diode D878 and Thyristor D862 work as Over Voltage Protectors. During normal operation, QE05-QE06 (Darlington configuration) are turned ON by the "Turn ON" Signal from the Microprocessor. This will supply a path for the +12V from the Stand-by Power Supply which will energize the Power Relay. If the +115V line increases excessively (15%), D878 will turn ON causing D862 to also turn ON. This will send +5V from the Stand-by Power Supply, through D862, to Q863. This will turn ON Q863 and the "Turn ON" signal from the Microprocessor will go to ground, thereby turning OFF QE05-QE06 and de-energize the Power Relay. Because the +5V line from the Stand-by Power Supply will continuously supply a current to the Thyristor D862, this Power Relay Shut-Off Operation will be held until the AC Power is disconnected. D862 will also turn ON if the output voltage of the Sub-power Circuit rises abnormally (detected by D837) or when the X-Ray Protection Circuit is actuated (detected by D472).

## MAIN POWER SUPPLY CIRCUIT

FIG. 3

-16-

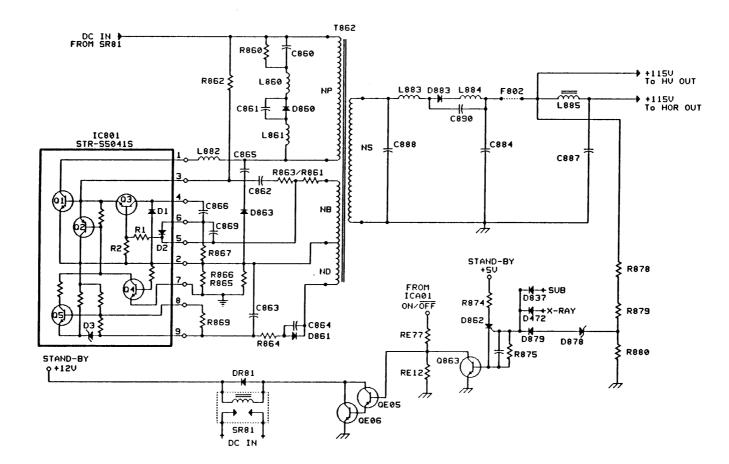

## SUB-POWER SUPPLY CIRCUIT

The Sub-power Supply Circuit produces +/-32V to be supplied to the Convergence Circuit Board, and +5V to be supplied to the PIP Circuit Board.

The limited availability of power that can be taken from the Main Power Supply Circuit is the reason why a Sub-power Supply Circuit is provided totally independent of the Main Power Supply Circuit. The Sub-power Circuit is a switching power supply made up of discrete components, but the basic principle of operation is identical to that of Standby and Main Power Supply Circuits.

Circuit discription is as follows;

Across the primary winding of T863, components D831, C833, and R833 make up a clamping circuit that will suppress any voltage spikes. R830 is the start-up resistor and Q803 is the main switching transistor. Q805 and D833 make the Q803 base current bypass circuit that will control the stability of the power supply. R831 and Q804 perform the over current protection operation.

On the secondary side of T863, the output of winding Ns2 goes through D834/C837 and make up the +32V rectifier circuit. The output of winding Ns3 goes through D835/C838 and make up the -32V rectifier circuit. Furthermore, the +32V source will be divided by R837 and R838 and then applied through D836,D837 to the gate of thyristor D862 for over voltage protection.

The output of winding Ns1 goes through D838/C848 and make up a +8V rectifier circuit. The +8V goes through a regulation circuit made up of Q806, D809 and C807. This will output +5V.

## SUB-POWER SUPPLY CIRCUIT

.

٠

FIG. 4

-18-

## NOTES

# III. SYSTEM CONTROL

-III-

## **TUNING SYSTEM**

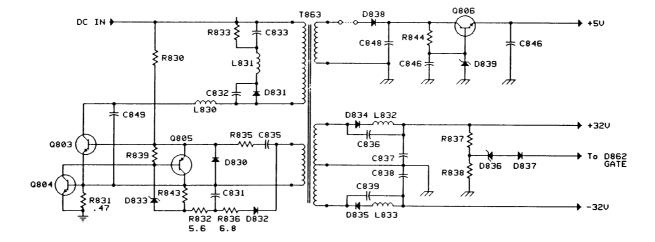

The projection TV tuning system performs frequency synthesized tuning and controls all TV set operations by using a newly developed single chip 4-bit microcomputer containing a built-in on-screen display character generating circuit.

A diagram of the tuning system is shown in the block diagram below (Fig. 1).

#### **Principal Features:**

- (1) Nominal channel capacity is 181 Channels (VHF, UHF, mid, super, hyper and ultra bands of CATV).

- (2) A D/A Converter IC (ICX01) is utilized to perform the audio/video digital control, thereby improving the performance of the circuit.

- (3) A microcomputer with a built-in on-screen display character generating circuit is adopted to perform the onscreen display, making the system compact.

- (4) System control of PIP operation is provided.

- (5) A port expansion IC (TA917P) has been adopted to up-grade the system.

**BLOCK DIAGRAM OF TUNING SYSTEM**

-21-

#### **TUNING SYSTEM (Cont)**

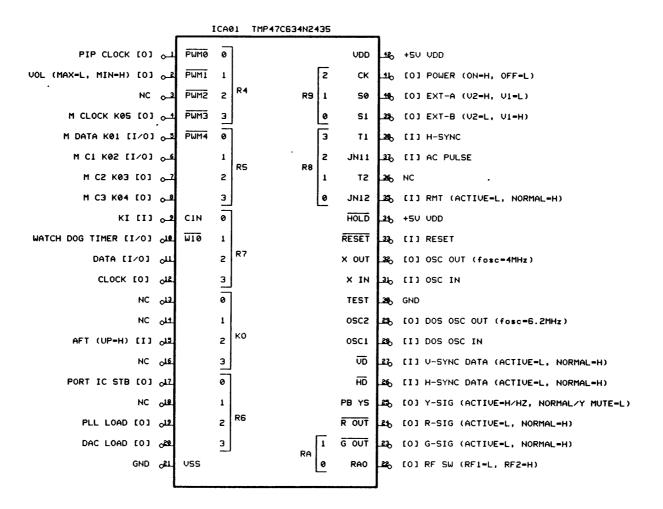

#### **Tuning Control Microcomputer**

A newly developed microcomputer (TM47C634N2435) having an on-screen display character generating circuit is used as the tuning control microcomputer. This microcomputer controls the entire system of the set as described below with priority given to the tuning process:

- (1) Front control panel input detection

- (2) Remote control transmitter input detection

- (3) Power ON/OFF

- (4) Audio and video digital control

- (5) Volume control

- (6) Carver ON/OFF

- (7) Multi-voice switching

- (8) Mute

- (9) Clock OFF timer

- (10) RF input switching

- (11) On-screen display control

- (12) PIP circuit control

- (13) Audio/video input switching

- (14) Port expansion IC control

- (15) Non-volatile memory control

- (16) CATV switching

- (17) Auto program, add/erase

- (18) Tuning process (10 keys, channel up/down)

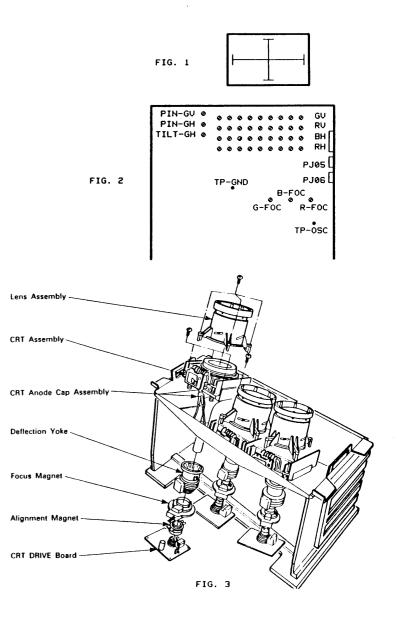

Pin names and functions of the microcomputer are shown (Fig. 2).

## **TUNING CONTROL MICROCOMPUTER**

FIG. 2

-23-

#### **TUNING SYSTEM (Cont)**

#### **Description of Tuning System Circuit Operation**

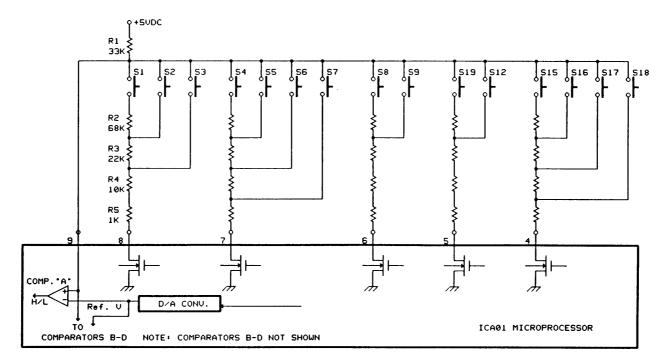

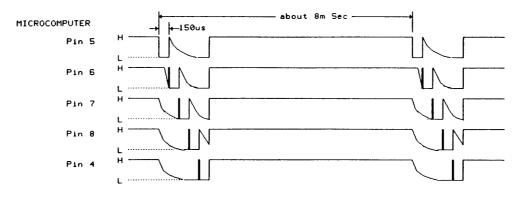

Front control panel input detection:

When key button switches on the front panel are pushed (see names of key button switches below), voltages obtained through voltage dividing resistors (R1-R5), shown in Fig. 3, input Pin 9 of the microcomputer. The circuit inside the microcomputer consists of a 3-bit D/A converter and a comparator. Variations of the input voltage level at Pin 9 of the microcomputer are detected by comparing it with the reference voltage and the output voltage from the 3-bit D/A converter.

As shown in Fig. 3, the key input detection is performed at five input blocks. For instance, if a key button is checked at Pin 8 (Block 1), Pin 8 of the microcomputer is held at earth potential and Pins 7 through 4 are in the floating state (at high impedance). This step is repeatedly carried out in order from Pins 8 to 4 of the microcomputer. If no key buttons are pushed, Pin 9 of the microcomputer is at +5V.

|      |          |      | _         |      |               |

|------|----------|------|-----------|------|---------------|

| SA01 | POWER    | SA06 | VOL UP    | SA12 | CARVER ON/OFF |

| SAO2 | TV/VIDEO | SA07 | VOL DN    | SA15 | AV FUNCTION   |

| SA03 | MTS      | SA08 | PROGRAM   | SA16 | AV RESET      |

| SA04 | CH UP    | SA09 | CATV      | SA17 | AV UP         |

| SA05 | CH DN    | SA19 | ADD/ERASE | SA18 | AV DN         |

|      |          |      |           |      |               |

#### **Timing Waveform**

## **KEY INPUT DETECTION CIRCUIT & TIMING WAVEFORM**

FIG. 3

-25-

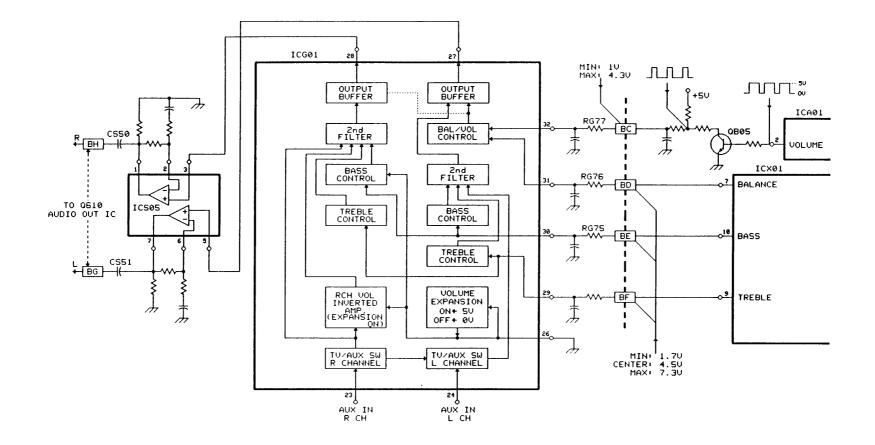

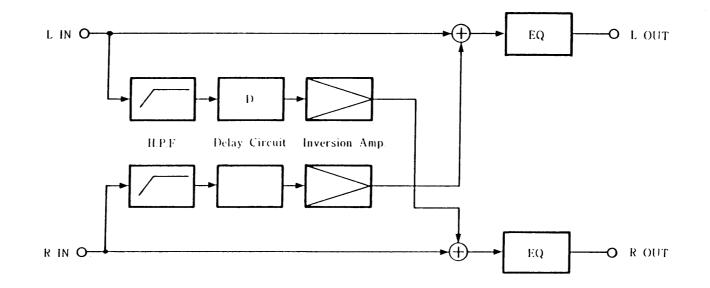

## AUDIO/VIDEO DIGITAL CONTROL

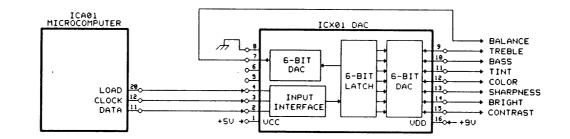

Audio/Video digital control is performed through the Digital to Analog Control (DAC) ICX01 (uPD6336C) by the Microcomputer (ICA01).

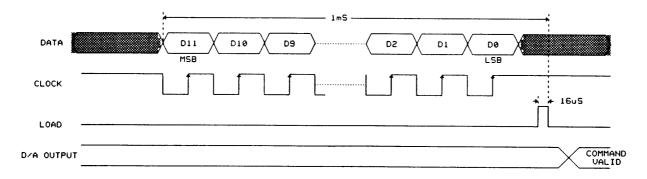

The contrast, brightness, sharpness, color and tint are controlled in the video circuit, while bass, treble and balance are controlled in the audio circuit. As shown in Fig. 4, the microcomputer transfers digital signals serially through three output terminals (DATA, CLOCK and LOAD) to the input interface circuit of the DAC IC.

The DAC IC latches the data and converts it into an analog signal by a ladder-type resistor group which has 64 step (6bits) resolution, and outputs control voltages from pins 7 through 15. This DC control at pins 7 through 15 can vary from about 0 volts to about 9 volts. Furthermore, in order to assure a stable operation of the DAC, the microcomputer will update the data periodically or if changes are made through the remote control.

| Pin No.<br>uPD6336C Signal |         | Terminal Name              | Functions                                                                                                                                                                            |  |  |  |  |

|----------------------------|---------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                          | Vcc     | Interface Power Supply     | Interface power supply for external control (Microcomputer, etc). Voltage same as the controller power supply.                                                                       |  |  |  |  |

| 2                          | DATA IN | Serial Data Input          | Data are read in synchronization with rising edge of the shift clock signal applied to input terminal of the control data and clock terminal.                                        |  |  |  |  |

| 3                          | CLOCK   | Shift Clock Input          | Clock terminal for data reading. Date applied to DATA IN terminal of the IC are read in at rising edge of the clock signal.                                                          |  |  |  |  |

| 4                          | LOAD    | Load Pulse Input           | Strobe input after serial data entry. When high level pulse is applied to LOAD terminal, data are latched in data latch of the D/A converter and in data latch of the option output. |  |  |  |  |

| 7                          | DA8     | D/A converter output 8     | D/A converter output 8. D/A converter output range is GND through VDD.                                                                                                               |  |  |  |  |

| 9-15                       | DA7-DA1 | D/A converter outputs 7-1  | D/A converter outputs 7 through 1                                                                                                                                                    |  |  |  |  |

| 16                         | VDD     | D/A Reference Power Supply | y Reference power supply (+) for D/A converter.                                                                                                                                      |  |  |  |  |

|                            |         |                            |                                                                                                                                                                                      |  |  |  |  |

## D/A TERMINAL LOGIC

## DAC CONTROL CIRCUIT & TIMING WAVEFORM

FIG. 4

## NON-VOLATILE MEMORY

The non-volatile memory ICA02 (M58659P) stores "last data" information such as Ch No., volume, color, etc. that is needed to return the TV system to the original state should the AC power be disconnected. To memorize the last data on items listed below, the channel select microcomputer is always reading and writing to the non volatile memory. This updates the data when operations are conducted through the remote control or by the key switches on the TV set. This non-volatile memory has a memory capacity of 512 bits and stores the data described below:

- (1) All Channel Memory

- (2) Power Source

- (3) CATV Mode

- (4) **RF Input**

- (5) Last Ch

- (6) Audio/video Digital Control

- (7) Carver

- (8) Volume

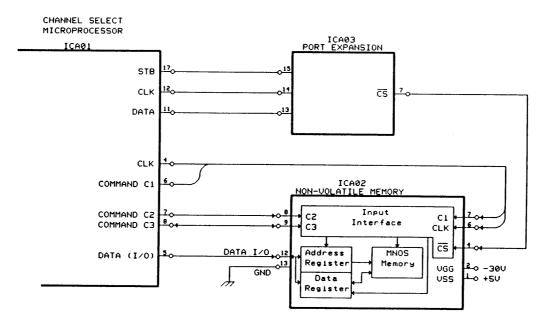

As shown in (Fig. 5), Data, Mode Change Pulses, and Clock Pulses output from pins 4 through 8 of the microcomputer to pins 6 through 9 and 12 of the non-volatile memory IC. Pin 5 of the microcomputer also serves as the input pin when reading data from the non-volatile memory.

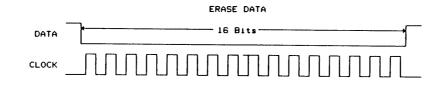

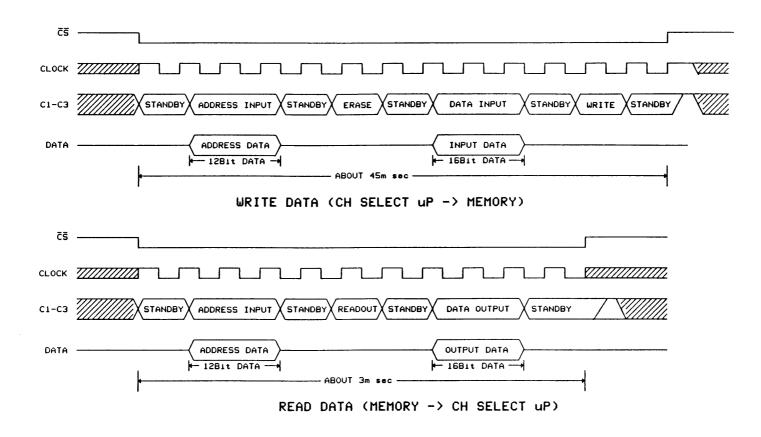

The Microcomputer controls the Port Expansion IC which in turn will output a Chip Selecting (CS) Signal through pin 7 to pin 4 of the Non-volatile Memory IC. The CS Signal will go "Low" during Data Write In/Data Readout. The Mode Change Pulses along with the Clock Pulses feed into the Input Interface of ICA02 and will toggle the memory between Data Read/ Write & Standby. The Data will be writing into the memory as Address Data (12-bit) and Input Data (16-bit). The control circuit of the Non-volatile Memory IC and the memory control timing waveforms are shown in the timing chart in the nexy page.

## NON-VOLATILE MEMORY CONTROL CIRCUIT

FIG. 5

-29-

### **READ/WRITE TIMING WAVEFORM**

| C1 | C2 | C3 | FUNCTIONS                                                                                                      |  |  |  |

|----|----|----|----------------------------------------------------------------------------------------------------------------|--|--|--|

| H  | H  | н  | STANDBY-address and contents of data register are held. Output buffer enters floating condition.               |  |  |  |

| н  | Н  | L  | DUMMY-not used.                                                                                                |  |  |  |

| н  | L  | н  | ERASE-contents of memory transistor in address designated by address register is erased.                       |  |  |  |

|    |    |    | The erase is equivalent to write "L" on all bits (16) at the designated address.                               |  |  |  |

| н  | L  | L  | ADDRESS INPUT- $I/O$ terminal data is transfered to address register & the address register is set.            |  |  |  |

|    |    |    | With this mode, 20 words address can be designated.                                                            |  |  |  |

| L  | Н  | н  | READOUT-contents of memory transistor at the address designated is transferred to data register.               |  |  |  |

| L  | Н  | L  | DATA OUTPUT-contents of data register is output in synchronization with the clock.                             |  |  |  |

| L  | L  | н  | WRITE-contents of data register is written on memory transistor at address designated by the address register. |  |  |  |

| L. | L  |    | DATA INPUT-I/O terminal write data is read in the data register. Contents of the address register is held.     |  |  |  |

-30-

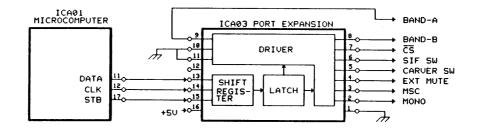

## **CONTROL OF PORT EXPANSION IC**

The purpose of the Port Expansion IC is to increase the control of the Microcomputer (ICA01) over the entire system.

Output ports of the Port Expansion IC (ICA03: TC9174P) are controlled by the Microcomputer through three control lines. These control lines are: DATA (Address Data [12 bit] and Output Data [16 bit]), CLOCK & STB.

In order to assure stable operation of the Port Expansion IC the microcomputer will update the data to the Port Expansion IC periodically or every time operations are conducted through the remote control or by key switches on the TV set. The control circuit of the Port Expansion IC is shown in Fig. 6.

Contents of the Port Expansion IC outputs:

- (1) Multi-voice Mode Switching

- (2) Carver ON/OFF

- (3) Ext Audio Mute

- (4) SIF Switching

- (5) Band Switching

- (6) Non-volatile Memory "CS Signal" output

#### PORTS OUTPUT LOGIC TABLE

| MULTIVOICE MODE SWITCHING |        |     |      |  |

|---------------------------|--------|-----|------|--|

|                           | STEREO | SAP | MONO |  |

| MCS (#3)                  | Н      | L   | Н    |  |

| MONO (#2)                 | L      | L   | Н    |  |

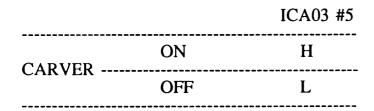

#### CARVER ON/OFF

|                | EXT AUDIO MUTE | ICA03 #4 |

|----------------|----------------|----------|

| EXT<br>AUDIO - | ON             | Н        |

| MUTE           | OFF            | L        |

#### SIF SWITCH

|        |     | ICA03 #6 |

|--------|-----|----------|

| SIF    | ON  | Н        |

| SWITCH | OFF | L        |

# BAND SWITCHING VL VH VH HYPER UHF

| TV        |   | VH |   |   | UHF | - |

|-----------|---|----|---|---|-----|---|

| BAND-A #8 |   |    | Н | Н | Н   | _ |

| BAND-B #9 | L | Н  | Н | Н | L   | - |

CATV

## PORT EXPANSION IC CONTROL CIRCUIT & TIMING WAVEFORM

FIG. 6

-33-

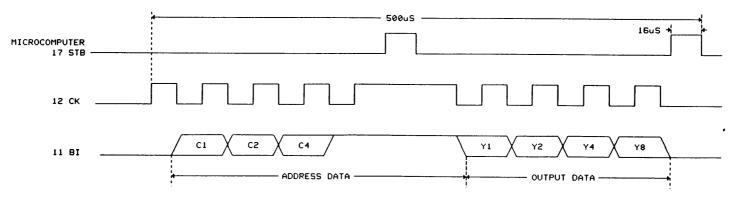

#### CONTROL OF A/V SWITCHING

The A/V Signal Switching Circuit's function is to switch incoming video and audio signals of the antenna and external inputs. This is performed at ICV01 (TA7717P) in the A/V Circuit. ICV01 is controlled by the Microcomputer (ICA01) through two control lines (EXT-S & EXT-B), see Fig. 7. TV, VIDEO 1/S-VIDEO, and VIDEO 2 are switched in the order shown by the logic table below. Video/audio outputs are also provided along with a Variable Audio Out.

| ICA01       | TV | VIDEO 1 | VIDEO 2 |  |

|-------------|----|---------|---------|--|

| EXT-A (#39) | Н  | L       | Н       |  |

| EXT-B (#40) | Н  | Н       | L       |  |

#### **THEORY OF OPERATION**

The detected video from IC101, enters the A/V Board and inputs switching ICV01 at pin 15. The input video signals (E1/S-Video and E2) enter ICV01 at pins 7 and 11 respectfully. The selected video will output at pin 25 and input ICS22 (Test Signal SW IC), through a clamp circuit and amp (QV12, 13 & 14). The signal now outputs the A/V Board and is coupled directly to the CCD Circuit. The chroma signal of the S-Video input is directly coupled to the S-Video switching circuit ICV40 on the CCD Board.

The TV Audio Signal (Lch, Rch) and each of the input audio signals (E1 & E2) also input ICV01 (see A/V Switching Block Diagram) and the selected input is coupled to the TV A/V Out and to the Carver PCB.

## **A/V SWITCHING CONTROL CIRCUIT**

-35-

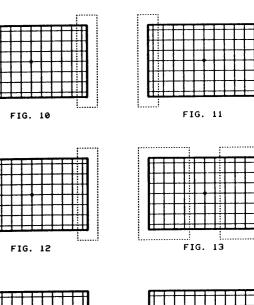

## **ON-SCREEN DISPLAY CIRCUIT**

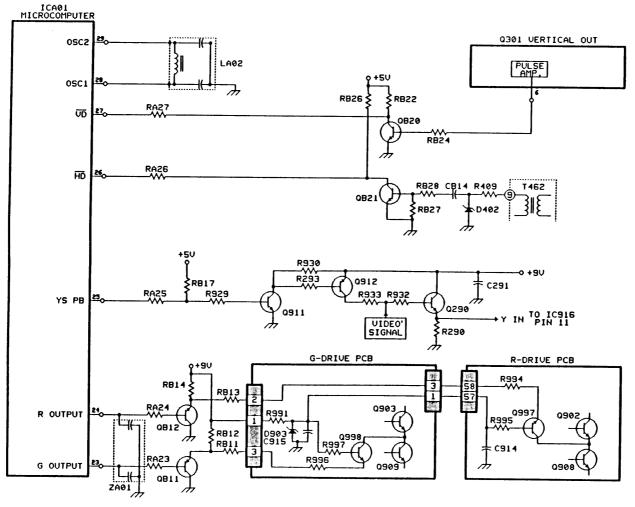

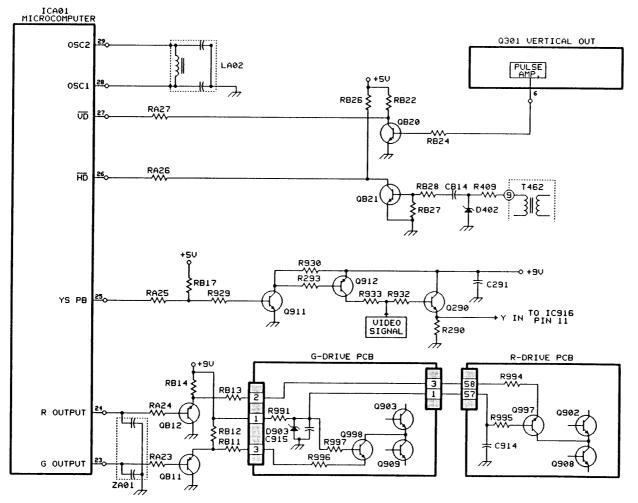

The On-screen Display Character Generator is contained within in and controlled by the microcomputer. It manipulates (by a program) the display of characters, display position, character sizes, character colors, display ON/OFF, and so forth. The generated signals output ICA01 through pins 23, 24, and 25. They are, Ys (positive logic), R (non-logic) and G (non-logic) Signals. The On-screen Display Circuit is shown in Fig. 8.

Contents of the On-screen Characters Display are;

(1) Ch # (RF-1)(6) CATV CH # & MODE (STD,HRC,IRC)(2) RF-2 Ch #(7) MTS MODE (STR,SAP,MONO)(3) MUTE(8) TIMER/CLOCK(4) VIDEO 1 or 2(9) A/V DIGITAL Control(5) VOLUME(10) PIP Source

The On-Screen Display Circuit requires three control signals: CLOCK, HD and VD.

The Clock Generator consist of the Oscillator IC (LA02). It inputs a 6.2MHz signal to pins 28 and 29 of ICA01, which is controlled by HD. The free run (HD=OFF) frequency of this oscillation circuit is 6.2 MHz.

VD (V sync Data) is needed to determine the vertical position of the on-screen display. The Vertical Sync Pulse outputs from the pulse amplifier at Q301 (AN5521) pin 6 of the Vertical Output Circuit. The signal is coupled through QB20 for polarity inversion and is applied to the microcomputer at pin 27.

HD (H sync Data) is needed to determine the horizontal position of the On-screen Display. The Horizontal Sync Pulse is taken from Pin 9 of the FBT (T462). The signal is inverted through QB21 and is applied to the microcomputer at pin 26.

-36-

## **ON-SCREEN DISPLAY CIRCUIT**

FIG. 8

-37-

#### **ON-SCREEN DISPLAY CIRCUIT (Cont)**

The Ys Signal is a positive logic signal (H Active) during On-screen Display. It is output from pin 25 of the microcomputer and cuts off the video signal by turning ON Q911 and Q912.

Additionally, since picture blanking is needed during "Power ON" and "Channel Selection", the Ys signal is also used during this time.

During on-screen display, the R Signal outputs the microcomputer through pin 24 and is resistance coupled to the base of QB12. The emitter of QB12 is connected to the emitter of Q997 through RB13 and R994 in the R-Drive PCB. The base of Q997 is supplied with a constant voltage of about 4.3V from the G-Drive PCB, and the collector of Q997 is connected to the intersecting point of Q902 and Q908 in the CRT drive circuit. As a result, when the R signal outputs from Pin 24 of the microcomputer, QB12 is turned ON. Accordingly, Q997 is turned ON and current flows to QB12 from Q997 through R994 and RB13, and the R signal from the On-screen Display Circuit is superimposed on the R-CRT Drive Circuit.

The G Signal output circuit has the same circuit configuration as that of the R Signal output circuit. When the G Signal outputs from Pin 23 of the microcomputer, QB11 is turned ON. As a result, Q998 of the G-Drive PCB is turned ON and current flows to QB11 from Q998 through R996 and RB11. Now the G Signal from the On-screen Display Circuit is superimposed on the G-CRT Drive Circuit.

## **ON-SCREEN CONTROL CIRCUIT**

FIG. 8

-39-

# NOTES

.

.

# IV. VIDEO/CHROMA PROCESSING

-IV-

## TUNER-PIF CIRCUIT OUTLINE

An RF signal induced on an antenna is converted into the intermediate frequencies of 45.75 MHz, for video and 41.25 MHz for audio within the tuner circuit. (Hereafter the intermediate frequency signals are called IF signals.) The IF signals are band-limited in passing through a SAW filter and are then detected by the PIF/SIF circuits, thus obtaining the video, audio, and AFT output.

Some of the major features in the tuner circuit includes;

1. The newly developed IC EL695LX1 (181CH) which includes a PLL circuit built within.

2. A wide band double surface acoustic wave filter (Z101) is used as the SAW filter.

3. A FS system is used for channel selection.

4. In the PIF/SIF circuits, PLL sync detection systems are employed, which results in the improvement of the following characteristics;

A. Telop buzz due to video over modulation is eliminated.

B. Improved reproduction characteristics of high frequency signal components are obtained.

C. Cross color distortion and interference is eliminated.

#### **PIF CIRCUIT**

-42-

## PIF CIRCUIT, AGC CIRCUIT

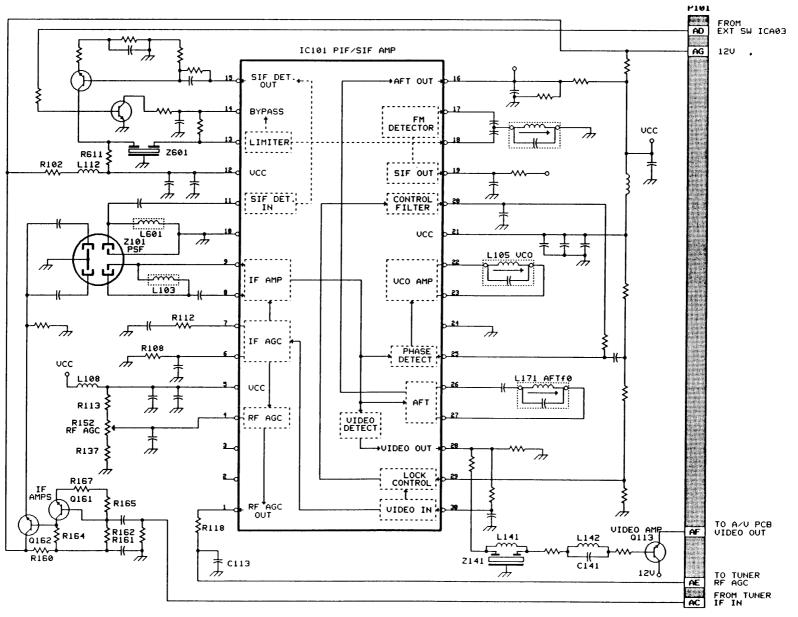

The PIF (Picture Intermediate Frequency) circuit amplifies and detects the IF signal from the SAW filter thus developing the video signal.

If a signal induced on the TV antenna varies in strength, the video detector output also varies. To prevent this, an AGC (Automatic Gain Control) circuit is provided to control the gain of the IF amplifier or the tuner, and thereby obtaining a constant output.

#### THEORY OF OPERATION

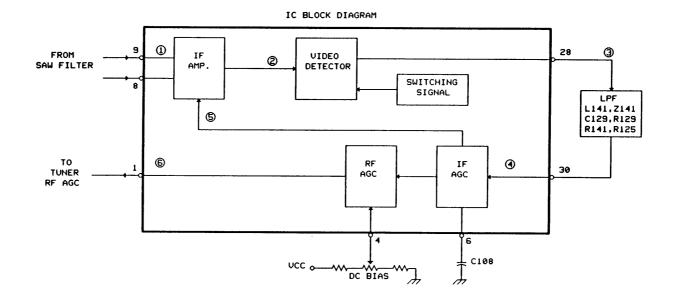

1. The IF signal corrected in its frequency response by the SAW filter is amplified at the IF Amplifier.

2. The amplified IF Signal is subject to multiplying detection with a Switching Signal (described in the PLL Circuit) to develop the video signal. Since phasing of the Switching Signal is -180 degrees from the IF Signal, the Video Signal is a negative sync type.

3. The video signal outputs the IC through pin 28.

4. The video signal is coupled through a LPF and then inputs the IF AGC circuit again with the harmonics eliminated.

5. The IF AGC circuit detects the sync tip voltage of the video signal fed back and thereby controls the gain of the IF amplifier. The IF AGC's time constant (response characteristic) is determined by C108 externally connected to pin 6 of IC101.

6. When the input field strength is high, the IF AGC circuit develops a control voltage for the RF AGC and varies AGC terminal voltage of the tuner, thus controlling gain of the amplifier inside the tuner. The field strength which starts operation of the RF AGC is determined by the DC bias supplied through pin 4 by R152 and applied to the RF AGC circuit. The RF amplifier is biased to operate at maximum gain. When the signal strength increases, the RF AGC voltage drops to decrease the gain of the RF amplifier (reverse RF AGC). The RF AGC voltage range is from +7V under weak signal conditions, to +1V for strong signal conditions. (Refer to RF AGC Delay adjustment.)

## **PIF/AGC CIRCUIT**

a na an

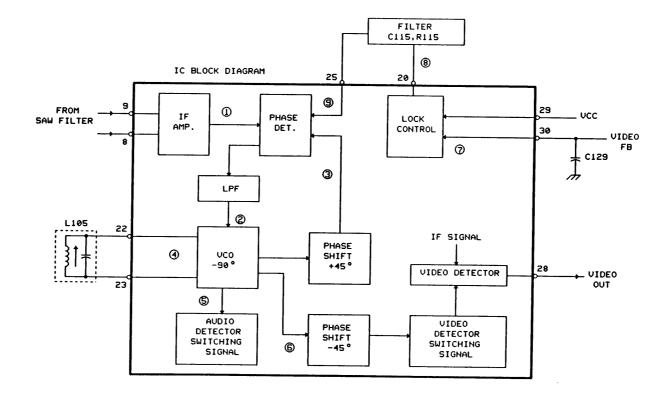

## PLL CIRCUIT

Detection operation is carried out incorporating a switching type detector to develop the Video and Audio Signals from the IF Signal. The PLL Circuit generates the Switching Signal.

In a conventional Quasi Sync Detection System, the Switching Signal is created by waveshaping the Video IF Signal. In the PLL Sync Detection System, the Switching Signal which has the same frequency as that of the Video IF Signal except for a specified phase difference is automatically generated.

#### THEORY OF OPERATION

1. The IF Signal is band-limited by the SAW Filter, amplified in IC101 and coupled to the Phase Detection Circuit.

2. A control voltage is applied to the VCO so that a phase difference of -90 degrees from the Video IF Signal is established.

3. The VCO output, (45.75MHz), passes through a +45 degree Phase Shift Circuit and again enters the Phase Detection Circuit. The VCO itself is locked at -135 degrees to the IF signal (-90 -45 = -135).

4. The reference frequency of the VCO is determined by adjusting the external coil L105. (VCO adjust.)

5. The Switching Signal for the audio signal detection is directly obtained from the VCO.

(Phase difference of the switching signal the audio signal detection is -135 degrees to the video IF signal.)

6. On the other hand, the switching signal for video signal detection is also obtained from the VCO, but its phase is shifted an additional -45 degrees. (As a result, the phase difference of the switching signal for the Video Signal is -180 degrees to the Video IF Signal (-135 -45 = -180).

7. The video signal is coupled back to pin 30 of Q101 and smoothed by external capacitor C129 before entering the Lock Control Circuit.

8. Presence or absence of the video signal is identified by observing the DC voltage from pin 30.

9. If a video signal does not exist, the external filter (pins 20 & 25) is controlled so that the pull-in frequency range of the Phase Detection Circuit is increased to search for a video signal. In the same way, when the video signal exist, the filter is controlled so that the pull-in range is reduced to eliminate noise pick-up.

## PLL CIRCUIT

-46-

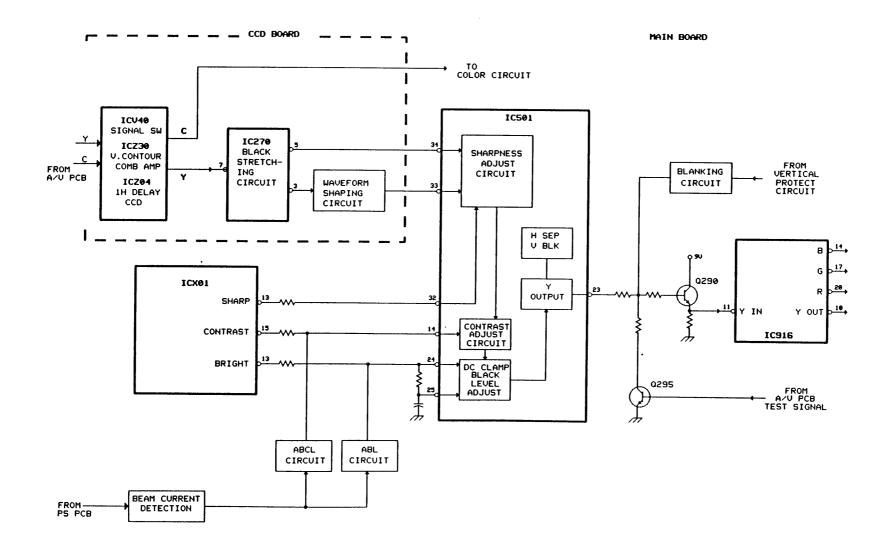

## **VIDEO PROCESSING OVERVIEW**

A composite video signal selected by the TV/Video Switching Circuit (ICV01) enters a CCD Comb Filter/ Vertical Edge Correction Circuit where the Y and C Signals are separated. The Y Signal is subject to black stretching and transmission rate correction in the Black Stretching Circuit, IC270. This processed Y Signal is then applied to pins 33 and 34 of IC501. Low and medium frequency components of the Video Signal input at pin 34, while pin 33 is the input terminal for high frequency components of the Video Signal.

After entering IC501 the Video Signal is then added to a Sharpness Control Circuit and then fed to a Contrast Adjustment Circuit. A sharpness adjustment voltage from ICX01 and the addition of the low and high frequency components within IC501 varies the D.C. voltage set at pin 32, thereby adjusting the sharpness.

An established voltage from pin 15 of ICX01 is applied to pin 14 of IC501 to vary the gain of the contrast adjustment circuit. This circuit also uses additional controls from the ABCL and ABL Circuits. The D.C. voltage at pin 24 establishes the pedestal level. The DC voltage generated at pin 25 varies the clamp level set by pin 14 of ICX01, thereby adjusting the black level.

The output of the Contrast Adjustment Circuit, DC Clamp Circuit, and Black Level Adjustment are then coupled through the Y-output Circuit and outputs at pin 23. Blanking pulses are added inside IC501, and the output from pin 23 is coupled through emitter follower Q290 to the Matrix Output IC916 pin 11. The output of IC916 pin 11 is coupled to the Video Amplifiers Q270/Q276 and then applied to the G-DRIVE PCB. Here the signal will be dispersed between the G, B, and R-DRIVE PCBs.

The "Y" Signal input is also mixed inside IC916 with the R-Y, G-Y, and B-Y Signals that input pins 15, 18, and 21 to develop the proper Red, Green, and Blue Drive Signals.

## **VIDEO PROCESSING BLOCK DIAGRAM**

.

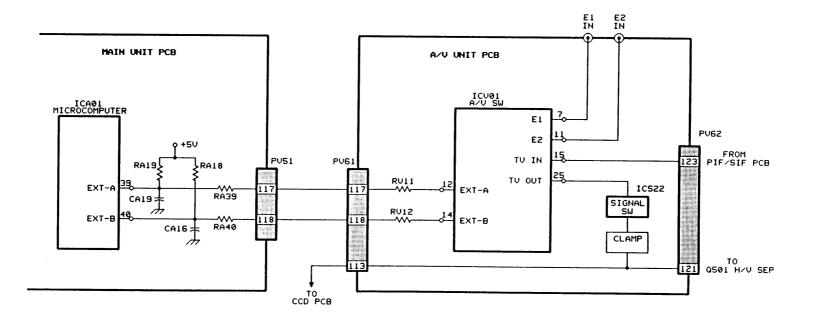

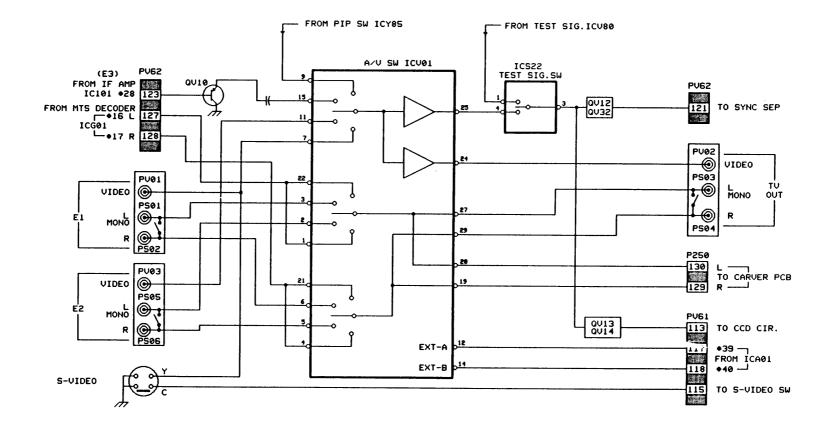

## **VIDEO/AUDIO INPUT SWITCHING CIRCUIT**

The Video/Audio Input Switching Circuits whose function is to switch the Video and Audio Signals of the antenna and external input signals (E1/S-VHS Video, E2 and Det. Output), consists of ICV01.

Each video input terminal provides one video input terminal and two audio terminals (L side is used as a mono jack) for each of the three available systems E1, E2, and S-VHS Video. If S-VHS Video is selected, then the audio terminals from E1 will automatically be selected as the audio input. Furthermore, the Y Portion of the S-Video Signal will enter ICV01 through pin 7 (same pin used by E1 Video Input).

A TV output terminal is also provided at the back of the unit.

#### THEORY OF OPERATION

The detected TV Video from IC101 is coupled to the A/V Board and inputs the Switching ICV01 at pin 15. Each of the Video Signals (E1/S-VHS, and E2) inputs ICV01 at pins 7, and 11, respectfully. The TV Audio Signal (Lch, Rch) and each of the Audio Signals of E1/S-VHS, and E2 also inputs ICV01 at pins 1 through 6. The output at pin 25 is coupled to the CCD Circuit by passing through buffer QV12, a DC Clamp Circuit, amplifier QV13, and QV14 Buffer Circuit.

The Chroma Signal of the S-VHS Video is directly coupled to the S Video (S-VHS) Switching Circuit ICV40 on the CCD Board.

All selected audio signals from each system are coupled to the Audio Control Circuits.

## **A/V SWITCHING BLOCK DIAGRAM**

-50-

and a second

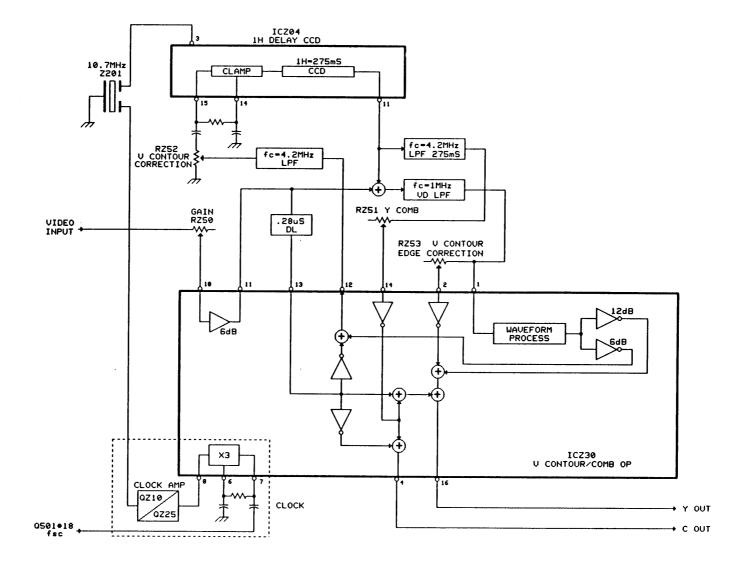

## **CCD VERTICAL CONTOUR CORRECTION AND COMB FILTER CIRCUIT**

The CCD Vertical Contour Correction Circuit consists of a 1H Delay and the associated circuits that perform vertical contour correction and Y/C separation. By using the CCD Circuit an increased frequency bandwidth of the video will be achieved. In addition, a clearer picture is obtained by combining the CCD with a concentrated electron beam CRT and a Wideband Video Output Circuit.

#### THEORY OF OPERATION

When the Composite Video Signal from QV14 on the A/V Input Switcher inputs pin 10 of ICZ30, it is increased by 6dB and outputs from pin 11. It then is split and one path is inductance coupled through a .28u sec. delay line XZ01. The signal inputs ICZ30 again at pin 13 where it is inverted and inputs ICZ04 pin 15 after being coupled through a LPF to eliminate harmonic distortion. After being delayed by 1H in the CCD Delay Circuit, the signal outputs at pin 11. It then is coupled through a 4.2 MHz LPF and inputs pin 14 of ICZ30.

The other signal path is added to the output of ICZ30 pin 11 for the filtering operation. This output is added to the signal that has been delayed by 1H, inverted and coupled through ICZ30. The added signals consist of the Edge Section, Color, and CCD Clock Components. The signal is then coupled through a VD Low Pass Filter (fc = 1MHz) to remove the undesired clock and color components. At this point the signal inputs ICZ30 at pin 2 where it is amplified and inverted. Within ICZ30, the developed signals are added together and are subjected to a waveshaping circuit for coring process, peak clip, and emphasis. At this time the Y and Chroma Signals are separated. Y outputs from pin 16 and the Color Signal from pin 4 of ICZ30 are DC coupled to pins 16 and 12 of the Signal SW ICV40.

The fsc (3.58 MHz) signal supplied from pin 18 of IC501 is capacitive coupled to pin 7 of ICZ30. Inside ICZ30 a tripler circuit converts the fsc signal into 3fsc to be used as the clock signal for the CCD.

# **CCD COMB FILTER & VERTICAL CONTOUR CORRECTION CIRCUIT**

-52-

T

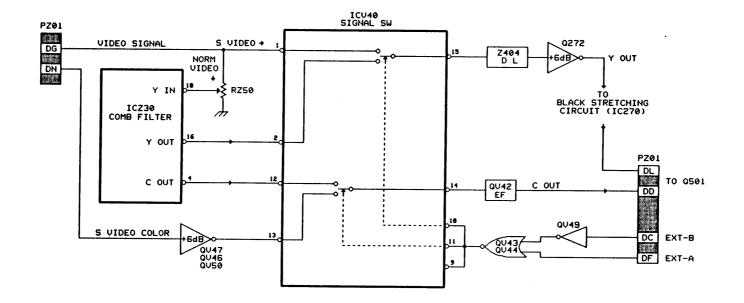

## **S-VHS VIDEO SWITCHING CIRCUIT**

The S-video (S-VHS) Switching Circuit consists of ICV40. ICV40 toggles Luminance and Chroma Signal Systems preceding or following the CCD Comb Vertical Contour Correction Circuit. Since the S-video Signal already has the Y and Color Signal separated it is not necessary to use the CCD Comb/Vertical Contour Correction Circuit for signal separation.

#### THEORY OF OPERATION

An EXT-A and EXT-B signal from microprocessor ICA01 inputs the CCD Board at DF and DC to be used as the S-video Switch Command. If the S-Video plug is conected to the back of the set, an internal switch (normally close to gnd.) will be pushed open and terminal DM (SW) at the CCD Board goes to high impedence (10V). Only when SW is at high impedence, the EXT-A is "L" and EXT-B is "H" will pins 9, 10, and 11 of ICV40 show "H" and place the IC in the S-video Mode. As a result, the incoming Y Signal enters pin 1 of ICV40 and is coupled directly to pin 15 of the same IC bypassing the CCD Comb Vertical Contour Circuit. From pin 15 the signal is coupled through the delay line XZ04 and 6dB amplifier Q272 and inputs the Black Stretching Circuit, IC270. At the same time, the S-color Signal entering the PC board at pin DN inputs ICV40 pin 13 after going through a 6dB amplifier circuit consisting of QV46, QV47, and QV50. Pin 13 is internally connected to pin 14, and the output S-color Signal is coupled through emitter follower QV42 to output the CCD Board at pin DD and input IC501 pin 31 on the Main Board.

When the EXT-A is not "L" and the EXT-B is not "H" (that is any combination other then), pins 9, 10, and 11 of ICV40 are set to "L" by NOR Circuit QV43 and QV44. In this, normal video condition, pins 2 and 12 of ICV40 are then connected to pins 15 and 14, respectively. The Y Signal from pin 15 is amplified about 6dB by Q272 and coupled through emitter follower Q271 to pin 7 of IC270 the Black Stretching IC.

The normal Chroma Signal at pin 14 is also coupled through emitter follower QV42, and follows the same signal path as the S-color Signal.

## S-VHS SWITCHING BLOCK DIAGRAM

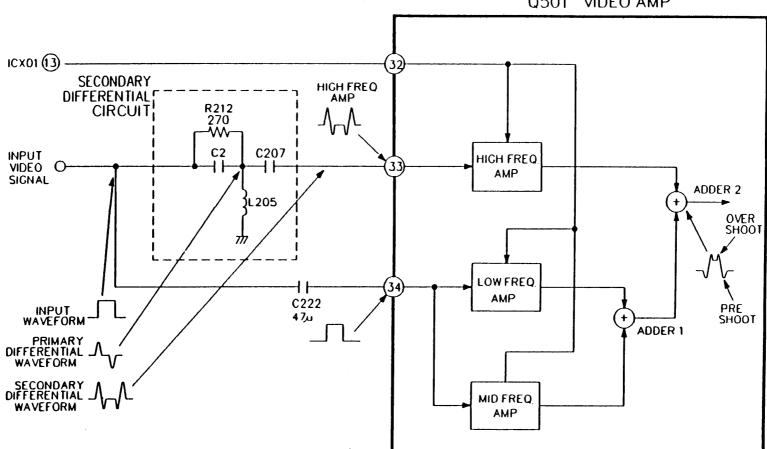

### PICTURE SHARPNESS ADJUSTMENT CIRCUIT

The Picture Sharpness Adjustment Circuit will superimpose a secondary differential waveform on edge portions of the luminance signal. This sharpens the rising and falling characteristics of the edge portions by using preshoot and overshoot effects, thereby giving a clearer definition at the boundaries of pictures.

#### THEORY OF OPERATION

The input signal supplied from the CCD PC Board inputs the Main PC Board at terminal DL to the Sharpness Circuit. It is first differentiated by C202, R212, and L205, and then again differentiated by C207.

The differentiated signal inputs pin 33 of IC501 to the Picture Sharpness Circuit. Pin 33 provides for the input of the high frequency components of the video signal. At the same time, the video input is coupled through C222 to block the DC component. This signal also inputs pin 34, the terminal for the medium and low frequency components of the video signal. Within IC501, the input at pin 34 passes through a Low Range Amplifier and then is combined in the Adder #1 Circuit.

Now returning to the high frequency signal input at pin 33, observe that it is coupled through a High Frequency Amplifier and then is sent to Adder #2 where it combines with the product of Adder #1. At this time, the preshoot and overshoot effects are in operation to give improved contrast characteristics to the edge parts.

A DC Voltage from pin 13 of ICX01 is used as the picture sharpness adjustment control. This control voltage is applied to pin 32 of IC501 to vary the gain balance among the High, Medium, and Low Amplifiers to obtain an optimum frequency response.

The Processed Video Signal is now ready to enter the Contrast Adjustment and the Black Level Adjustment Circuits within IC501. After DC restoration and pedestal clamping, the Y Signal outputs IC501 at pin 23. Blanking pulses are added and this processed signal is coupled to the Y-output Amplifier Q290 and Matrix Control IC916. The Y Signal then will output the Main Board at connector 93 to be directly coupled to the CRT-DRIVE PC Boards.

## PICTURE SHARPNESS ADJUSTMENT BLOCK DIAGRAM

Q501 VIDEO AMP

-56-

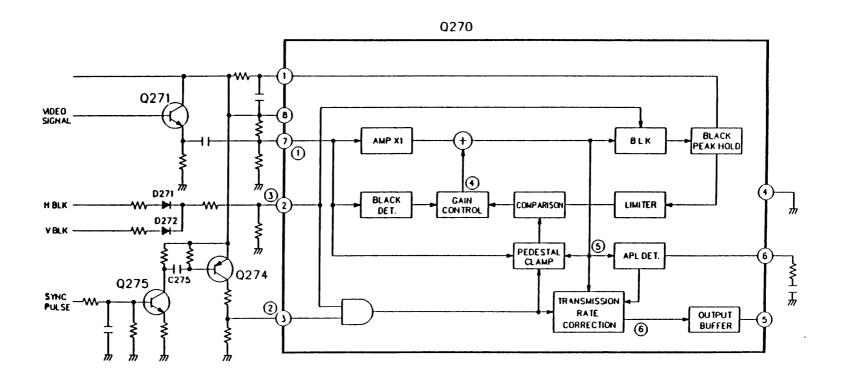

## **BLACK STRETCHING CIRCUIT**

The Black Stretching Circuit (located on the CCD PCB) is utilized in order to improve the contrast ratio by "stretching" the black most portion of the video signal to equal the pedestal level. It consists of IC270 and associated circuits.

The input signal from the Video Switching Circuit (emitter of Q271) enters at pin 7 of the Black Stretching IC. A sync signal developed at IC501, pin 28 (Video-Color IC) is waveshaped by Q275, C275, and Q274 and coupled to the input pin 3 of the Black Stretching IC. A blanking pulse (Horizontal and Vertical) is coupled through their respective OR Gates, D271 and D272 and is applied to IC270, pin 2.

When a video signal enters the Black Stretching IC it passes through three types of circuits: Black Peak Hold, Black Detection, and Pedestal Clamp. Each of the outputs are compared and the difference voltage is used as a gain control. The gain control manages only the part of the video signal closes to the black level.

The Sync Pulse and H/V Blanking are used in the Transmission Rate Correction Circuit. This circuit maintains the proper control voltage to preserve the relationship between the Pedestal Level and the Average Picture Level (APL) of the video.

The results of these circuits in the Black Stretching IC insure that the black level is processed and clamped solid with respect to pedestal level for a clearer picture with vivid blacks.

The output of the Black Stretching Circuit at pin 5 of IC270 is then coupled to pins 33 and 34 of IC501.

## **BLACK STRETCHING CIRCUIT**

-58-

.

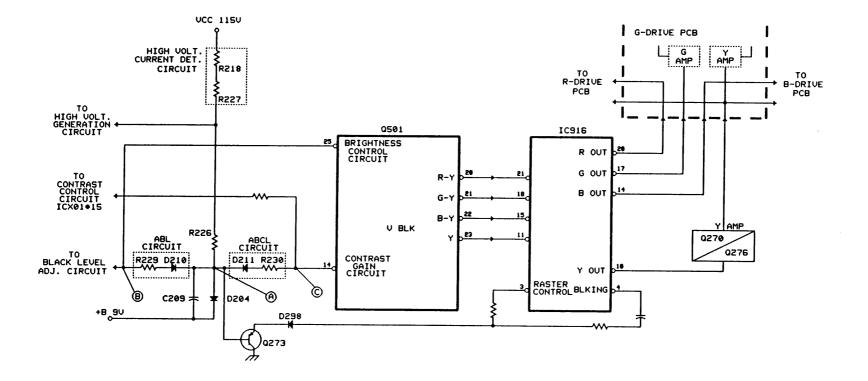

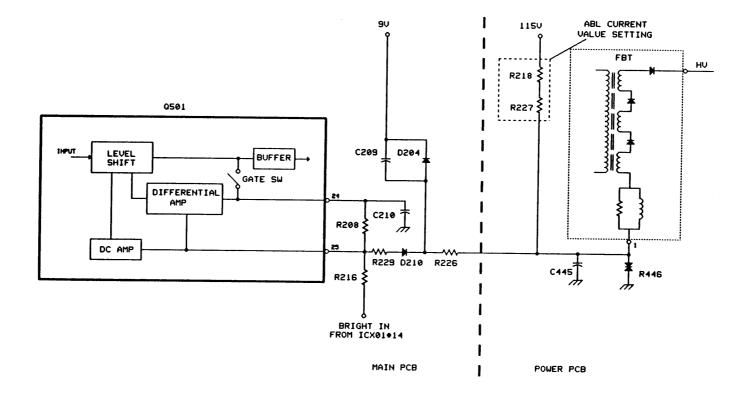

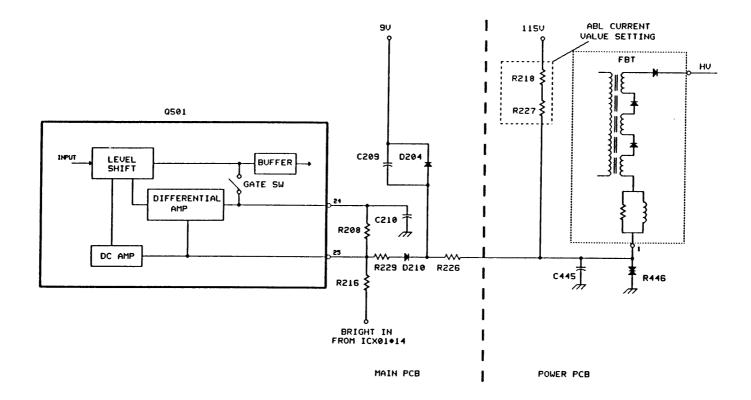

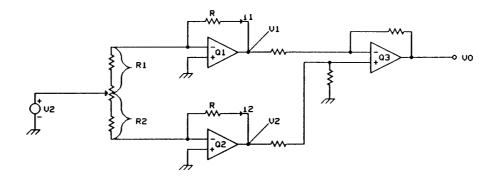

## AUTOMATIC CONTRAST ADJUSTMENT CIRCUIT (ABCL CIRCUIT)

To provide the picture with the desired contrast level, the Contrast Adjustment Circuit varies the AC level of the Video Signal and along with the ABCL Circuit will automatically reduce the contrast of a saturated Average Picture Level (APL) Signal to avoid deterioration in the linearity of black to gray response. In other words, improving the graduation quality of black tones.

#### THEORY OF OPERATION

Referring to the figure below, R218 and R277 (located on the Power Supply PCB), detect current flowing into the anode of the picture tube. When the APL (Average Picture Level) increases, beam current increases and the voltage drop across R218 and R277 also increases. As a result, positive voltage at point <u>A</u> decreases and D210/D211 become forward biased.

With D210 conducting, the brightness control voltage at pin 25 of Q501 (point B) is clamped to the D.C. voltage at point A and the gain of the Black Level Adjustment Circuit is lowered thereby reducing the high voltage current. In this manner, the ABL Circuit protects the picture tube, flyback transformer, and the Horizontal Output Circuit by holding the high voltage below the maximum limitations of the beam current.

At the same time, when D211 conducts current flows into R230 and the voltage at point  $\underline{C}$  lowers to less than 5V, thus decreasing the gain of the Contrast Circuit.

If the ABCL Circuit were removed and only the ABL Circuit existed, a high DC bias to decrease conduction of the CRT would be necessary to suppress the high voltage current that develops when a bright picture signal is present. This high DC bias, however, would lower the graduation quality of black tones. By using the ABCL Circuit to lower the AC gain of the video signal, a lower DC bias is needed to reduce the DC level of CRT conduction. The combined circuitry allows a constant brightness to contrast ratio impervious to changes in APL.

## **ABCL BLOCK DIAGRAM**

-60-

#### **BLACK LEVEL ADJUSTMENT CIRCUITS**

(Pedestal clamp, DC Restoration, ABL Circuit)

In TV receivers, the use of direct-coupled amplifiers are difficult because the gain from the detector output to the cathode of a picture tube is generally between 30 to 40dB, so capacitor coupled amplifiers are generally used.

In capacitive-coupled systems, the D.C. characteristics of capacitors cause pedestal level to vary with Average Picture Level (APL). As a result the black level also changes and this prevents precise reproduction of the signals broadcasted (DC restoration 0%). By suppressing the pedestal level variations due to the APL changes, the signal can be reproduced with 100% DC restoration and no brightness variations occur as the picture pattern changes. However, when the APL is low most of the video information exists near the black level, and when the APL is high most of the information exists near peak white. Since picture contrast differs considerably between the two cases, DC restoration is normally set between 70 and 90%. The DC restoration is managed after the pedestal level is clamped.

Additionally, to maintain the reliability of the picture tube, FBT, and horizontal output circuit, the ABL circuit limits picture brightness by detecting beam current.

# BLACK LEVEL ADJUSTMENT BLOCK DIAGRAM

-62-

1. N.

#### **BLACK LEVEL ADJUSTMENT CIRCUIT (CONT.)**

#### **Theory of Operation**

#### Pedestal Clamp Circuit

Pedestal clamping is necessary to maintain a stable black reference level. The pedestal clamp circuit is entirely contained within IC501. The video signals entering IC501 at pins 33 and 34 have a pedestal level that will vary with the APL. A differential amplifier is used in IC501 to insure that the pedestal level equals the difference between the black level voltage set by R216 and a DC voltage that corresponds to the pedestal level input at pin 25.

#### **DC Restoration Circuit**

While DC restoration (clamping) is handled within IC501, the amount of restoration ratio can be determined by R208. If R208 was increased in value (open), the black level and pedestal level would remain the same regardless of APL. In other words, the pedestal level would be maintained at a constant level and a 100% DC restoration ratio is obtained. However, if R208 were to decrease in value (short), no pedestal correction would be carried out and the DC restoration ratio is 0%. Therefore, by selecting a particular resistance value for R208, the DC restoration ratio can be optimize.

#### **ABL Circuit**

ABL operation is carried out by D210/D204 and the high voltage current that flows from the 114V line through R218 and R277. Whenever the beam current is low along with a low Average Picture Level (APL), the voltage drop across R218/R277 is low. This causes the voltage at the cathode of D210 (at point D) to rise to a higher value and D210 turns off suspending ABL operation and allowing current to flow through the forward biased diode D204.

When beam current increases along with APL, the voltage drop across R218/R277 and at the cathode of D210 (point D) increases. D210 is now properly biased and turns ON while D204 turns off. The video signal is now biased towards less conduction and beam current is adjusted to a lower value.

## BLACK LEVEL ADJUSTMENT BLOCK DIAGRAM

-64-

.

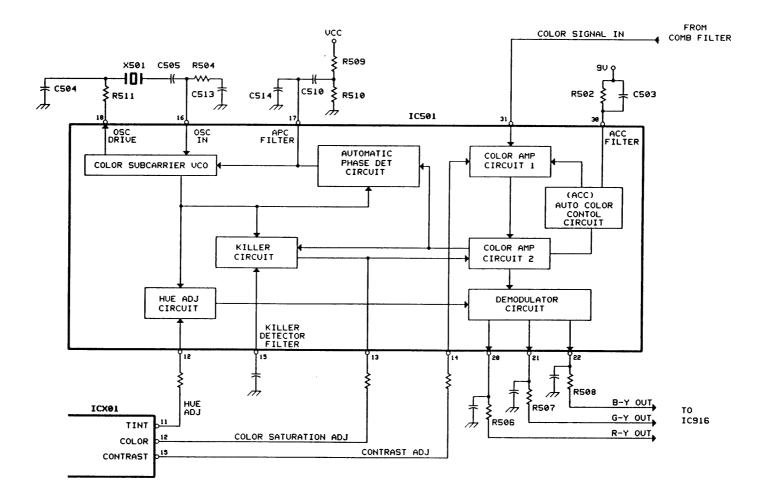

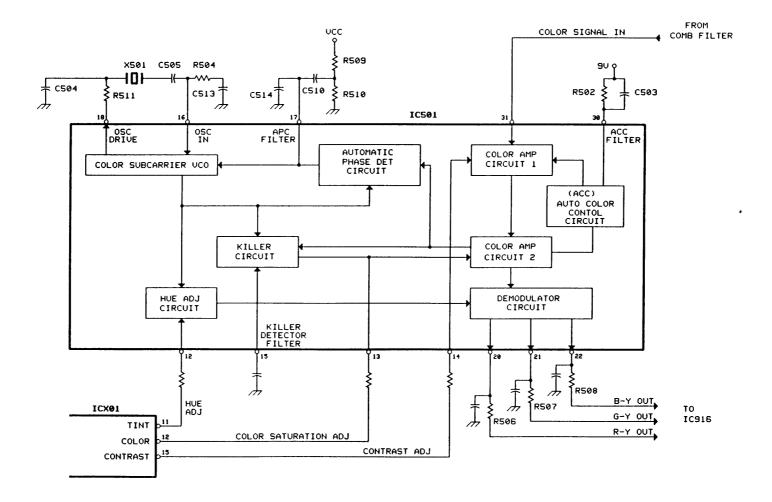

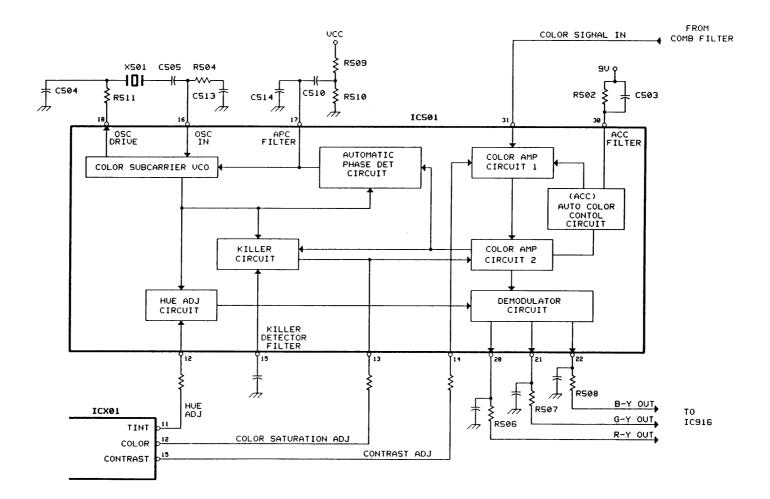

## **CHROMA SIGNAL PROCESSING**

#### **CHROMA AMPLIFIER**

The color signal processing circuit is almost entirely contained whithin IC 501.

The circuits and functions inside IC501 include; Chroma Amplification, Chroma ACC (Automatic Color Control), APC, Hue Adjustment, Color Kill Detection, 3.58 MHz Oscillator, Burst Amplifier and Color Demodulation.

The selected Chroma Signal output of SW ICV40, is coupled through an emitter follower QV42 on the Comb Filter Board and inputs the Main PCB where it is coupled through a band-pass filter consisting of C501, C502 & L501, to pin 31 of IC501. The signal is amplified by the first and second chroma amplifiers, that are controlled by the ACC, Color Killer, APC, etc.

### **CHROMA ACC**

ACC is accomplished by sampling the amplitude of the burst pulse at the output of the 2nd Chroma Amp. Circuit discription is as follows;

The Burst Signal is rectified into a DC voltage by the ACC Circuit and is used to control the gain of the first Chroma Amplifier. C503 & R502 connected to pin 30 serve as a filter for the DC voltage and keep the ACC voltage being applied to the First Chroma Amplifier constant and not subject to noise or instantaneous signal fluctuations.

## **CHROMA PROCESSING IC**

-66-

### 3.58 MHz OSCILLATOR & A.P.C.

The 3.58 MHz Sub Carrier Re-insertion Signal is necessary to demodulate the Red, Green and Blue Chroma Signals applied to the Demodulator Circuit. Simple phase demodulation occurs at the Chroma Demodulator.

In order to reconstruct the original chroma signal broadcast, it is necessary to phase lock the 3.58MHz oscillator signal generated in IC501 to the phase of the incoming Burst Signal. This is accomplished by sampling the burst signal from the Second Chroma Amplifier and phase comparing it to the output of the Color Sub Carrier VCO. Any phase difference develops a DC correction voltage which is applied to the Color Sub Carrier VCO. The main frequency determining components of the 3.58MHz Oscillator are R511, C504, R504, C513, X501 and C505

The phase locked 3.58 MHz Oscillator Signal is then applied through a Hue Adjustment Circuit and finally to the Demodulator Circuit.

#### HUE ADJUSTMENT CIRCUIT

A variable D.C. voltage at pin 12, established by ICX01, causes the phase of the 3.58 MHz Reinsertion Sub Carrier to be shifted. To perform hue correction, the Sub Tint Control connected to pin 12 of IC501 adjusts the preset phasing of the Hue Control Circuit.

## **CHROMA PROCESSING IC**

-68-

#### DEMODULATOR

The demodulator compares the phase of the incoming Chroma Signal from the Second Chroma Amplifier to the phase of the 3.58 MHz Sub Carrier Signal. The resulting output at pins 20, 21 & 22 of IC501 are the reconstructed R-Y, G-Y and B-Y Chroma Signals.

These signals are directly coupled to the Matrix output IC916 pins 15, 18, and 21. Here the chroma signals mix with the Luminance Signal applied at pin 11 thus developing the Red, Green and Blue Drive Signals applied to the CRT cathodes.

#### **COLOR KILLER**

The Color Killer Detector Circuit functions to turn "OFF' the Second Chroma Amplifier during a B/W broadcast by detecting the presence or absence of burst present at the Second Chroma Amplifier.

During a color broadcast, the Color Killer detects the presence of burst present at the Second Chroma Amplifier. The Color Killer is turned "OFF" which causes the voltage at pin 15 to go high, or approximately 9 volts.

When a B/W program is received, there is no burst signal present at the Second Chroma Amp. The Color Killer detects this and turns "ON" to turn "OFF" the Second Chroma Amp. With the Color Killer "ON", the voltage at pin 15 drops to about 5.5 volts.

## CHROMA PROCESSING IC

-70-

## NOTES

V.

## **PICTURE IN PICTURE**

-V-

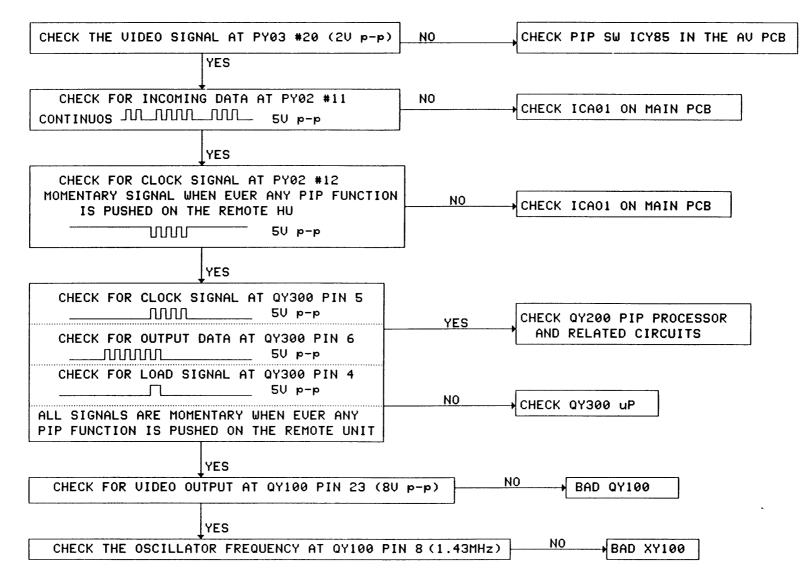

## PIP (SUB-PICTURE) SYSTEM

Toshiba's Picture-in-Picture has greater versatility then ever before. PIP features include:

SIZE: The PIP can be changed from 1/4 to 1/16

SWAP: The main picture and PIP picture can be exchanged.

STILL: The PIP picture can be frozen.

CHANNEL SEARCH: A PIP picture of four channels in sequence will appear at the bottom of the screen.

POSITION CHANGE: The PIP picture can appear in any corner of the screen.

SEQUENTIAL SEARCH: Four frames will advance with a progression of still frame images.

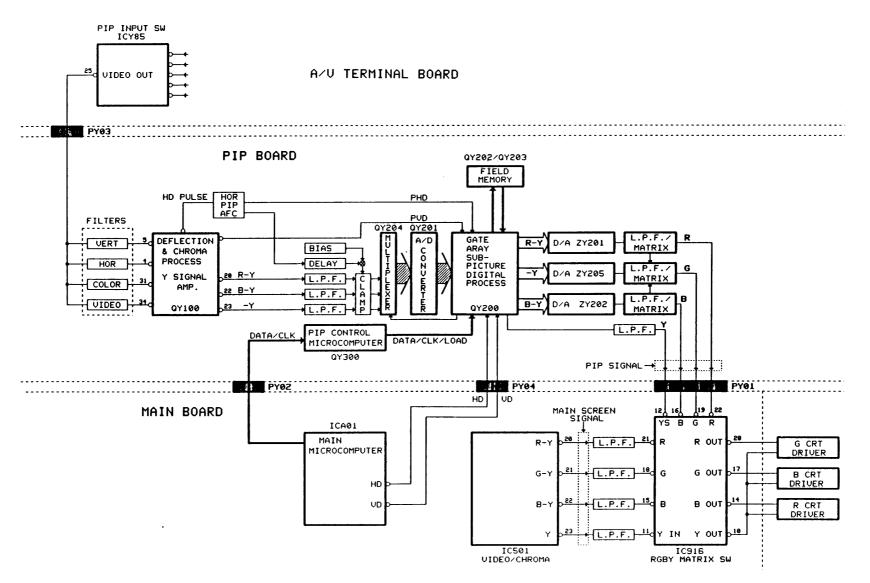

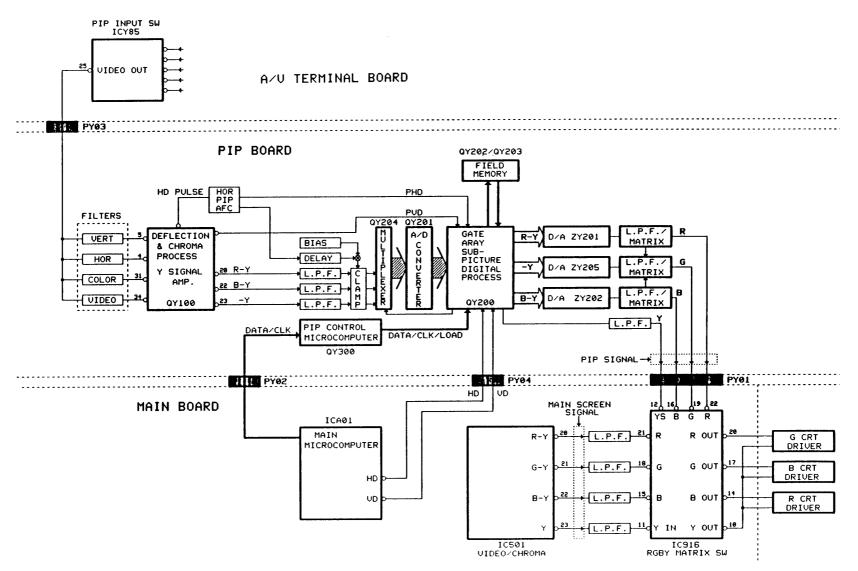

The PIP System is contained on the PIP Board UX01. This circuit will change Sub-picture Video Signals into Analog RGB Signals. This signal is then inserted into the main picture. The block diagram of the PIP System is shown in Fig. 1.

Here the PIP system is described by dividing it into the following 4 sections:

- I. Circuits involved in video/chroma processing of the input video signals.

- II. Circuits involved in digital processing of converted digital signals for analog conversion.

- III. Circuits involved in output of luminance and color difference signals as RGB signals.

- IV. Microcomputer interface circuit for operating digital circuits.

## PIP SYSTEM BLOCK DIAGRAM

-73-

.

### PIP CIRCUIT (Cont.)

#### **VIDEO/CHROMA PROCESSING UNIT**

This Sub-picture System consist of a circuit that converts video signals into the Luminance Signal (Y) and Color Difference Signals (R-Y, B-Y), and inserts them into the Main Picture. In this section the Video/Chroma Processing Circuit of the PIP system is described along with signal flow. Refer to Fig. 1 which shows the block diagram of the PIP system and the RGB Circuit.

#### THEORY OF OPERATION

Video/Chroma Processing

QY11 performs Video/Chroma processing, PIP Video Signal contol, and V/H psuedo sync processing. The Video Signal Output from the Sub-picture AV Switching Circuit, inputs to pins 33 & 34 of QY100, after removal of the color signal components. The color signal inputs the IC through pin 31. RY103 and CY100 make up an integration circuit used for Vertical Sync separation at pin 5. RY100 and CY101 make up an integration circuit used for horizontal sync separation at pin 4. Contrast, Hue, Shade and Brightness are also regulated in the Video Chroma Circuit. The Y Signal is output at pin 23, while R-Y and B-Y Signals are output from pin 20 and 22 respectively.

Sub-picture Sync Signal Generating Circuit

The Sub-picture Sync Signal Generating Circuit is concentrated around the Video/Chroma IC QY100. A Sub-picture Vertical Sync Signal (PVD) is produced by shaping the output signal from pin 36 of QY100 by Vertical Driver QY103. The Sub-picture Horizontal Sync Signal (PHD) is developed at the Horizontal AFC Circuit by using pseudo-flyback pulses as a stabilized sync signal. When the switching transistor QY102 is turned ON by the horizontal drive pulses (HD) that output pin 10 of QY100, a pseudo-flyback pulse is developed through the resonance of CY131 and LY104. The flyback pulses are integrated by RY148 and CY134 and the resulting sawtooth pulses obtained input pin 6 of QY100. This way a stable AFC sawtooth operation is performed. The PHD signal finally outputs after passing through the wave shaping transistor QY104.

## **VIDEO/CHROMA PROCESSOR**

-75-

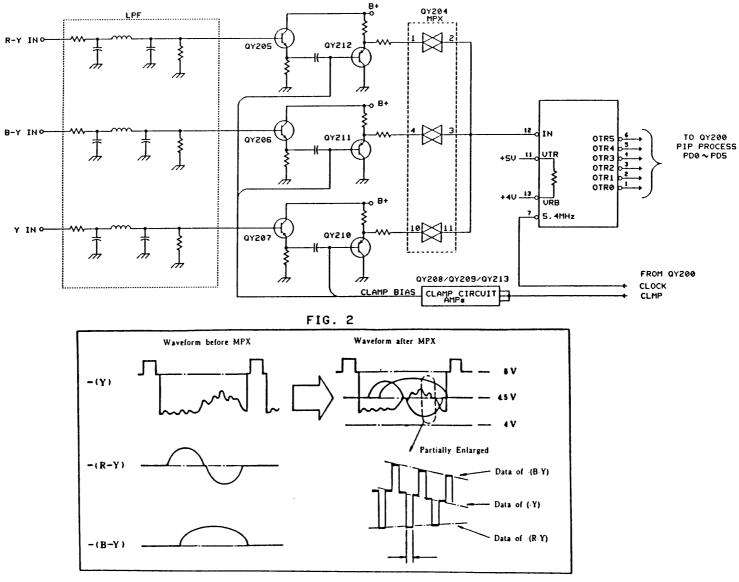

#### PIP (SUB-PICTURE) SYSTEM (Cont)

In this system the circuit digitally converts Y Color Differential Signals and displays them as pictures in reduced size (sub-picture display).

Pin names and functions of the Gate Array are shown in Table One.

### THEORY OF OPERATION

#### A/D Converter

The -Y, R-Y and B-Y Signals which are supplied from the Video/Chroma Processing IC are pre-processed in this circuit before being input to the A/D Converter QY201, (See Fig. 2). All three input signals are coupled through a Low-pass Filter Block where band limiting is performed. The value of the low-pass filters are 1.3MHz for -Y and .5MHz for the R-Y/B-Y signals. Band limiting is done to prevent the generation of "Conversion Noise" (Fold over Noise) which occurs at the time of A/D conversion. The pre-processed signals are then applied to a Clamp Circuit which consist of transistors QY205 through QY213.

In the Clamp Circuit the pedestal level is set so that the input signals are clamped accurately to the input range of A/D Converter (1v p-p max.). Clamped signals are then coupled through the Multiplexer (MPX) QY204 and inputs through pin 12 of the A/D Converter as Time Sharing Data. Shown in Fig. 3 is the concept of this MPX. The data is input to the A/D Converter at regular intervals of; -Y, -(R-Y), -Y, -(B-Y), -Y and -(R-Y) signals, and so on.

The A/D Converter IC takes the input analog signal and converts it into a 6-bit PCM Signal. The Clock Frequency (pin 7) is 5.4 MHz, and is coupled from pin 96 of the PIP Processor IC. An external bias circuit supplies IC QY201 with the input comparison voltages of 5V at pin 11(VRT) and 4V at pin 13(VRB). This gives the IC a 1 volt input range which is divided into 63 steps. This processed signal outputs as 6-bit data. These output signals (D1->D6), are now coupled to the PIP Processor IC.

## A/D CONVERTER & MPX CONCEPT

-77-

#### PIP (SUB-PICTURE) SYSTEM (Cont)

#### THEORY OF OPERATION

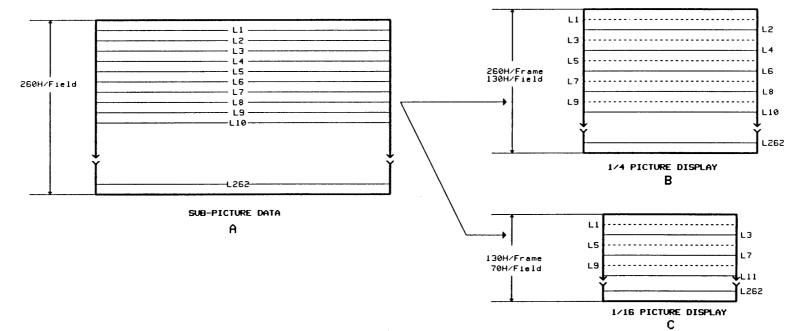

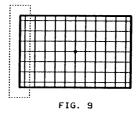

Figs. 4 and 5 show the quantity of data written on the sub-picture and quantity of data displayed on the main picture. Fig. 4(a) shows that sub-picture video (Y) is written into memory as 260H/Field. One field of memory out of each frame of the sub-picture video data is useful data for processing. Fig. 4(b) and (c) show the state where the sub-picture is displayed synchronously with the main picture.

In the case of Fig. 4(b), the circuit is using 260H/Frame and thereby will display 130H/Field (1/4 Picture Size Display); 1(1), 1(3), 1(5) and so on are displayed in the odd field of the main picture and 1(2), 1(4), 1(6) and so on are displayed in the even field of the main picture.

In the case of Fig. 4(c), the circuit is using 130H/Frame and thereby will display 65H/Field (1/16 Picture Size Display) data is read and displayed from memory by skipping over 1 line in both the horizontal and vertical directions. So that 1(1), 1(5), 1(9) and so on are displayed in the odd fields and 1(3), 1(7), 1(11) and so on are displayed in the even fields.

Fig. 5 shows the state of the write/read video data in the multi-mode. Fig. 5(a) shows that video data for the sub-picture is written as 130H/Frame, same as 1/16 Picture Size Display. In this mode, video from one field of each frame is useful data. Fig. 5(b) shows that the sub-picture is read and displayed at 65H/Field according to the odd fields and the even fields of the 1/16 Size Picture.

## WRITE/READ OF 2 & MULTI VIDEO DATA

FIG. 4

FIG. 5

## TABLE ONEGATE ARRAY PIN NAMES AND FUNCTIONS

| PIN NAME |        | <u>I/O</u> | <b>FUNCTIONS</b>                  | PIN | PIN NAME |     | FUNCTION                  |  |

|----------|--------|------------|-----------------------------------|-----|----------|-----|---------------------------|--|

|          |        |            |                                   |     |          |     |                           |  |

| 1        | VDD    | Ι          | +5V Power Supply                  | 25  | OTR3     | 0   | R-Y Output                |  |

| 2        | RST    | Ι          | Hardware Reset                    | 26  | OTR2     | 0   | R-Y Output                |  |

| 3        | VDD    | Ι          | +5V Power Supply                  | 27  | OTR1     | 0   | R-Y Output                |  |

| 4        | VD     | Ι          | Vertical Sync Input for Display   | 28  | OTR0     | 0   | R-Y Output                |  |

| 5        | HD     | Ι          | Horizontal Sync Input for Display | 29  | OTB5     | 0   | B-Y Output                |  |

| 6        | CS     | Ι          | Clamping Pulse Input              | 30  | OTB4     | 0   | B-Y Output                |  |

| 7        | PVD    | Ι          | Vertical Sync Input for Writing   | 31  | OTB3     | 0   | B-Y Output                |  |

| 8        | PHD    | Ι          | Horizontal Sync Inpt for Writing  | 32  | OTB2     | 0   | B-Y Output                |  |

| 9        | DATA   | Ι          | CPU Interface Data Input          | 33  | OTB1     | 0   | B-Y Output                |  |

| 10       | CK     | Ι          | CPU Interface Clock Input         | 34  | OTB0     | 0   | B-Y Output (LSB)          |  |

| 11       | LATCH  | I          | CPU Interface Latch Input         | 35  | OTY5     | 0   | Y Output (MSB)            |  |

| 12       | R      | 0          | Output for Pedestal Clamping Time | 36  | OTY4     | 0   | Y Output                  |  |

|          |        |            | Constant                          | 37  | OTY3     | 0   | Y Output                  |  |

| 13       | С      | Ι          | Input for Pedestal Clamping Time  | 38  | OTY2     | 0   | Y Output                  |  |

|          |        |            | Constant                          | 39  | OTY1     | 0   | Y Output                  |  |

| 14       | NTSCN  | Ι          | NTSCN/PAL Switching               | 40  | VSS      | Ι   | GND                       |  |

| 15       | VSS    | Ι          | GND                               | 41  | VDD      | Ι   | +5V Power Supply          |  |

| 16       | POSCI  | Ι          | Display OSC Circuit Input         | 42  | ΟΤΥΟ     | 0   | Y Output (LSB)            |  |

| 17       | POSCO  | 0          | Display OSC Circuit Output        | 43  | MD00     | I/O | Field Memo Data Y10 (LSB) |  |

| 18       | CONCKN | Ι          | Clock Source Switching            | 44  | MD01     | I/O | Field Memo Data Y11       |  |

| 19       | COSCI  | Ι          | Writing OSC Circuit Input         | 45  | MD02     | I/O | Field Memo Data Y12       |  |

| 20       | COSCO  | 0          | Writing OSC Circuit Output        | 46  | MD03     | I/O | Field Memo Data Y13       |  |

| 21       | VSS    | I          | GND                               | 47  | MD04     | I/O | Field Memo Data Y14       |  |

| 22       | YSOUT  | I          | YS Signal Output                  | 48  | MD05     | I/O | Field Memo Data Y15 (MSB) |  |

| 23       | OTR5   | 0          | R-Y Output (MSB)                  | 49  | MD06     | I/O | Field Memo Data Y20 (LSB) |  |

| 24       | OTR4   | 0          | R-Y Output                        | 50  | MD07     | I/O | Field Memo Data Y21       |  |

PIN NAME I/O FUNCTION

Field Memory Data Y22 **MD10** I/O51 Field Memory Data Y23 I/O 52 MD11 Field Memory Data Y24 MD12 I/O 53 Field Memory Data Y25 (MSB) 54 MD13 I/O Field Memory Data R-Y0 (LSB) 55 MD14 I/O Field Memory Data R-Y1 56 MD15 I/O Field Memory Data R-Y2 I/O 57 **MD16** Field Memory Data R-Y3 MD17 I/O58 Field Memory Data R-Y4 59 MD20 I/O Field Memory Data R-Y5 (MSB) 60 MD21 I/O Field Memory Data B-Y0 (LSB) MD22 I/O 61 Field Memory Data B-Y1 62 MD23 I/O Field Memory Data B-Y2 MD24 I/O 63 Field Memory Data B-Y3 64 MD25 I/O +5V Power Supply VDD 65 Ι GND VSS 66 Ι Field Memory Data B-Y4 **MD26** I/O 67 Field Memory Data B-Y5 (MSB) 68 **MD27** I/O Field Memory Address (LSB) A0 0 69 Field Memory Address 0 A1 70 Field Memory Address A2 0 71 Field Memory Address 0 72 A3 Field Memory Address 73 A4 0 Field Memory Address A5 0 74 Field Memory Address 0 75 A6

PIN NAME I/O FUNCTION

Field Memory Address 0 A7 76 Field Memory Address 77 **A8** 0 Field Memory Address 78 A9 0 Field Memory Address A10 0 79 Field Memory Address 0 A11 80 Field Memory Address 0 A12 81 **Field Memory Address** 82 A13 0 Field Memory Address (MSB) A14 0 83 IC Check Terminal 84 TEST I Field Memory Write Control R/W 85 Ι Picture Positionl Software Switch SOFTCN I 86 **Capicity Switching** ME2P 87 I AD Converter Data Input (LSB) PD0 Ι 88 AD Converter Data Input 89 PD1 I **GND** VSS 90 I +5V Power Supply VDD Ι 91 AD Convertert Data Input I 92 PD2 AD Convertert Data Input PD3 Ι 93 AD Convertert Data Input PD4 94 I AD Convertert Data Input (MSB) PD5 Ι 95 AD Convertert Clock Output ADCK 0 96 Multiplexer Y Signal Selection MPY 0 97 Multiplexer R-Y Signal Selection MPR 0 98 Multiplexer R-Y Signal Selection MPB 0 99 Pedestal Clamping Pulse Out 0 100 CLMP

## NOTES

# VI.

# MTS BROADCASTING SYSTEM

-VI-

## **MTS BROADCASTING SYSTEM**

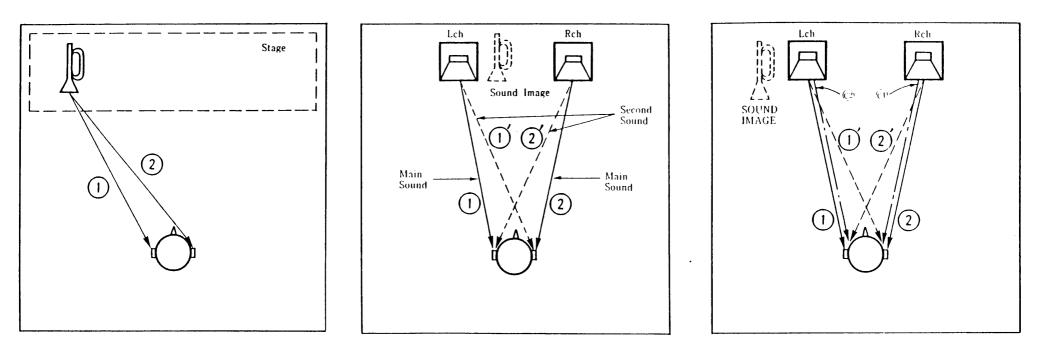

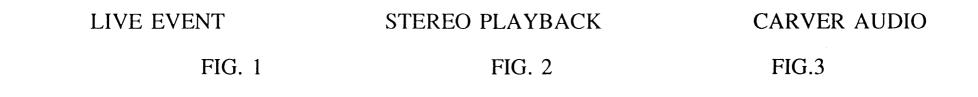

The North American audio multiplex broadcasting system allows simultaneous broadcasting of a monophonic sound, stereophonic sound (hereafter called stereo sound) and a separate audio program sound (hereafter called SAP).

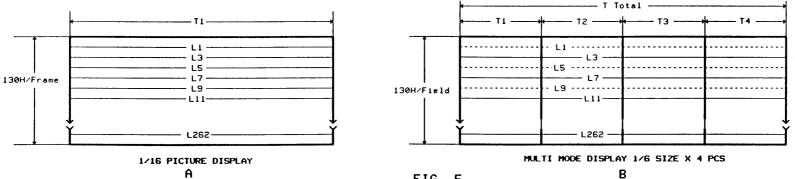

In this system, MTS carves four information channels out of the 120KHz audio baseboard, hence the term multichannel, instead of merely stereo. Listed below is the layout of the four channels.

#### Main Channel (mono)

The main channel is the same as current broadcast systems. Here we have good old mono information, with a few kilohertz sliced off the top end to allow room for the MTS pilot, at 15.734kHz (the horizontal scan rate). Deviation is  $\pm$  25kHz, with a pre-emphasis of 75us.

Noise reduction is not employed considering the compatibility of conventional receivers.

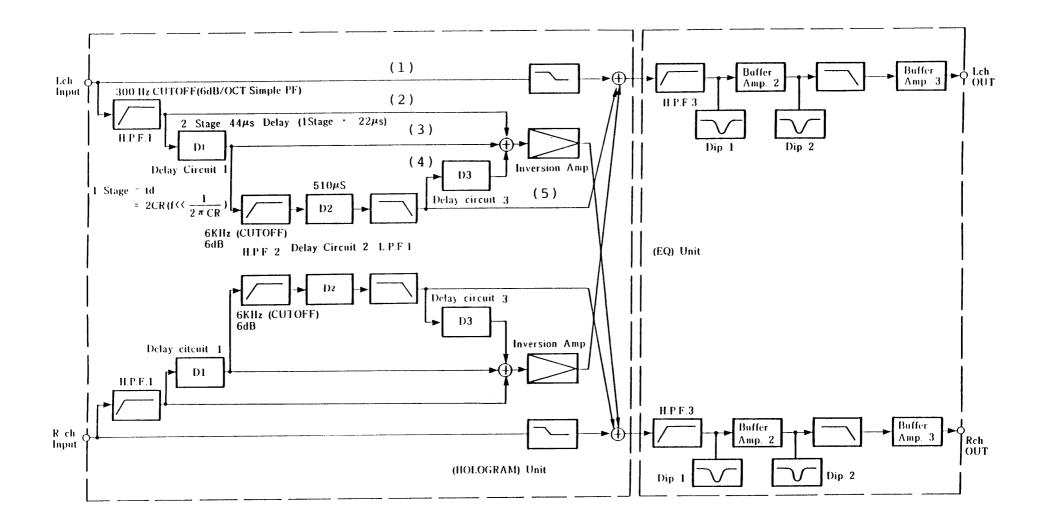

#### **1st SUB Channel (stereo)**